Intel PXA26X User Manual

Page 555

Intel® PXA26x Processor Family Developer’s Manual

16-7

Network/Audio Synchronous Serial Protocol Serial Ports

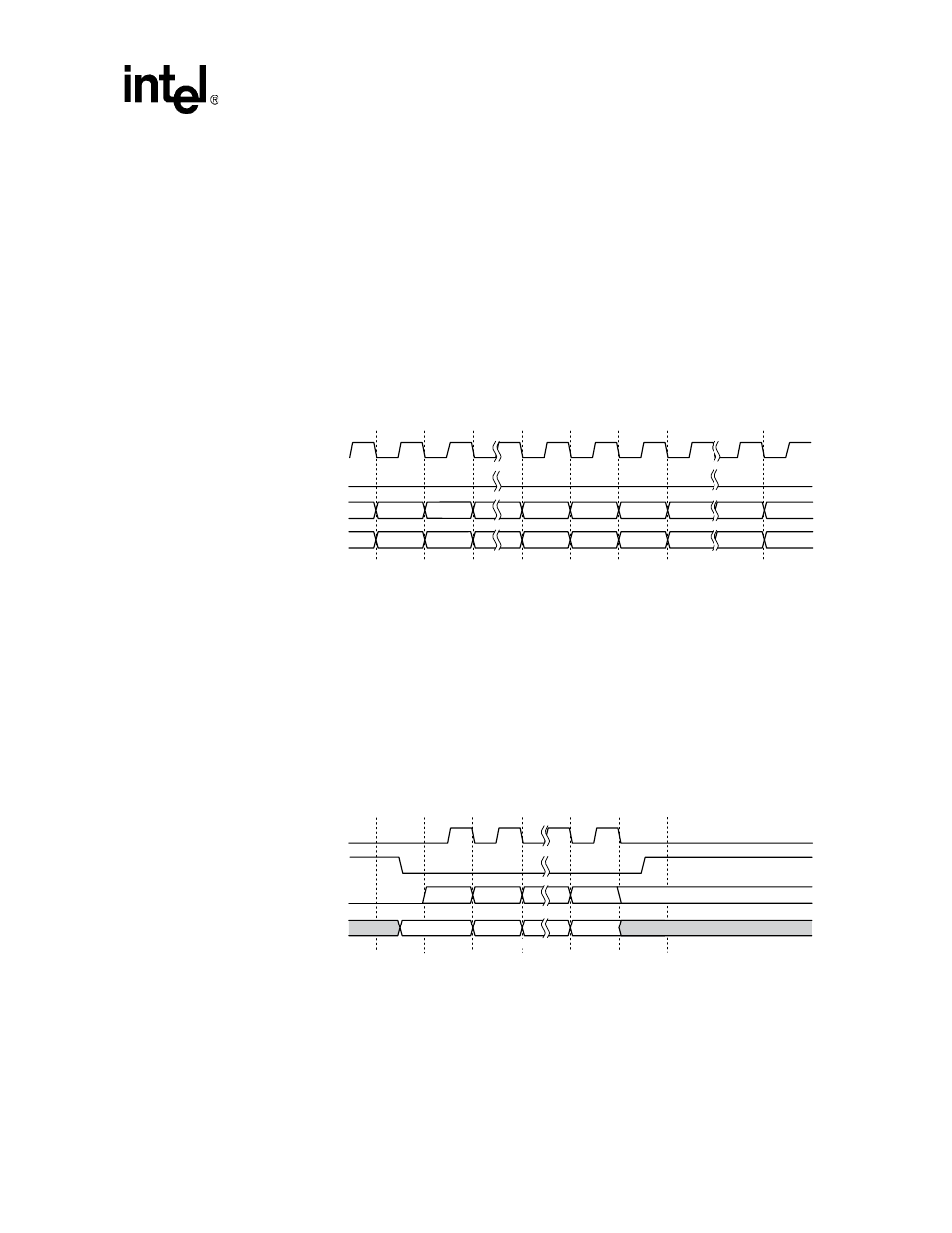

For back-to-back transfers, frames start and complete similar to single transfers, except SSPSFRM

does not de-assert between words. Both transmitter and receiver are configured for the word length

and internally track the start and end of frames. There are no dead bits; the least significant bit of

one frame is followed immediately by the most significant bit of the next.

When using the SPI protocol, the SSP port can either be a master or a slave device. However, the

clock and frame direction must be the same. For example, the SSCR1[SCLKDIR] and

SSCR0[SFRMDIR] must both be set or both be cleared.

shows when back-to-back frames are transmitted for the Motorola SPI* frame

shows one of the four possible configurations for the Motorola SPI* frame

protocol for a single transmitted frame.

Note:

When configured as either master or slave (to clock or frame) the SSP port continues to drive

SSPTXD with the last bit of data sent (the LSB). If SSCR0[SSE] is cleared, SSPTXD goes low.

The state of SSPRXD is undefined before the MSB and after the LSB is transmitted. For minimum

power consumption, this pin must not float.

Note:

The phase and polarity of SSPSCLK can be configured for four different modes. This example

shows just one of those modes (SSCR1[SPO] = 0, SSCR1[SPH] = 0).

Note:

When configured as either master or slave (to clock or frame) the SSP port continues to drive

SSPTXD with the last bit of data sent (the LSB). If SSCR0[SSE] is cleared, SSPTXD goes low.

Figure 16-3. Motorola SPI* Frame Protocol (multiple transfers)

Figure 16-4. Motorola SPI* Frame Protocol (single transfers)

A9651-01

SSPSCLK

SSPSFRM

Bit[N]

Bit[N-1]

Bit[0]

Bit[N]

Bit[N-1]

Bit[1]

Bit[0]

Bit[0]

SSPTX

SSPRX

Bit[1]

Bit[0]

Bit[N]

Bit[N-1]

Bit[0]

Bit[N]

Bit[N-1]

Bit[1]

Bit[0]

Bit[0]

Bit[1]

Bit[0]

A9519-02

SSPRXD

SSPSFRM

SSPSCLK

SSPTXD

MSB

LSB

Bit[N]

Undefined

Undefined

End of Transfer Data State

Bit[N-1]

Bit[1]

Bit[0]

Bit[N]

Bit[N-1]

Bit[1]

Bit[0]

4 to 32 Bits