Intel PXA26X User Manual

Page 223

Intel® PXA26x Processor Family Developer’s Manual

6-33

Memory Controller

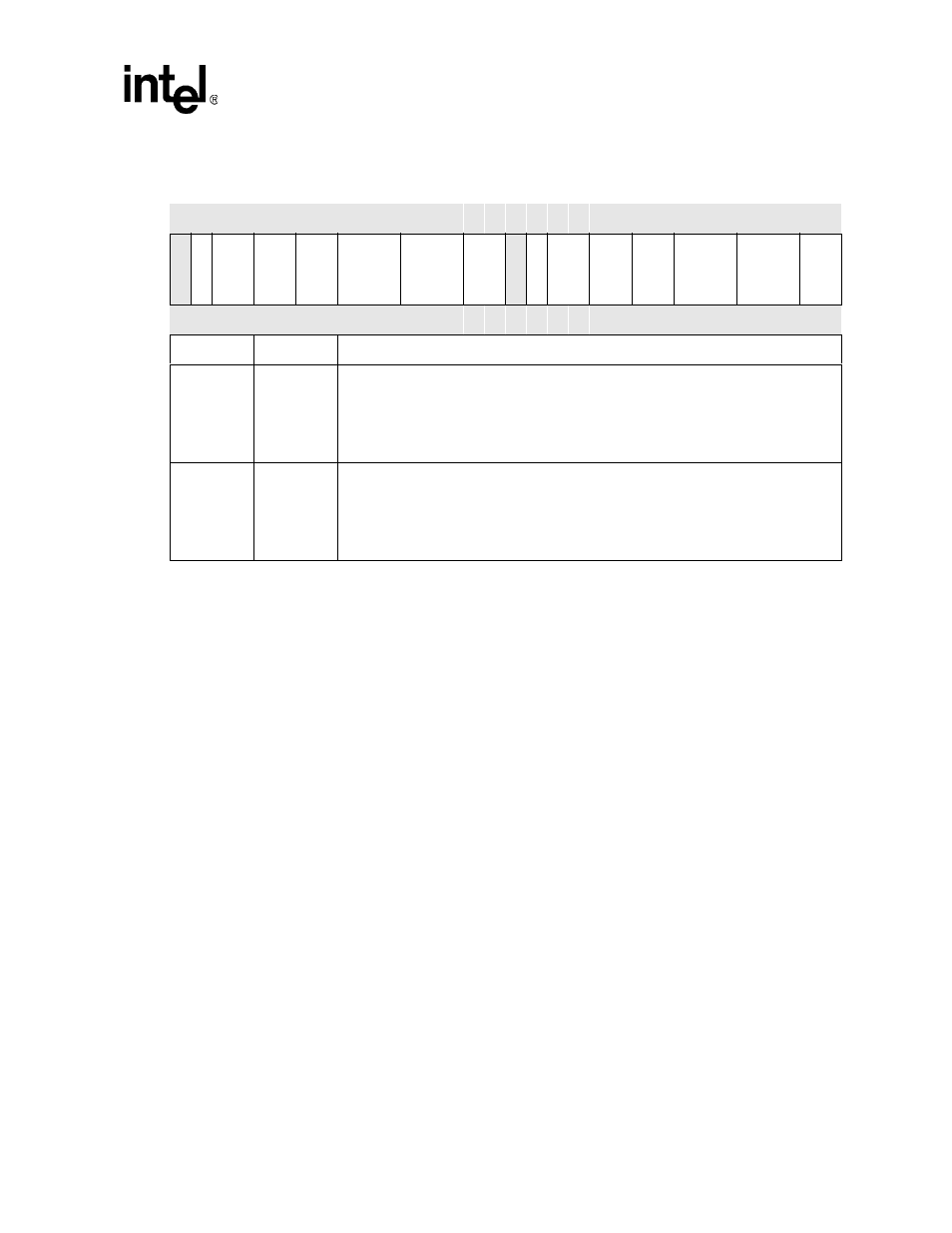

11:10

SXCA0

SX MEMORY COLUMN ADDRESS BIT COUNT FOR PARTITION PAIR 0/1:

00 – 7 column address bits

01 – 8 column address bits

10 – 9 column address bits

11 – 10 column address bits

9:8

SXRA0

SX MEMORY ROW ADDRESS BIT COUNT FOR PARTITION PAIR 0/1:

00 – 12 row address bits

01 – 13 row address bits

10 – Reserved

11 – Reserved

Table 6-14. SXCNFG Register Bitmap (Sheet 4 of 6)

4800 001C

SXCNFG

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

R

eser

ved

S

X

LA

TC

H

2

SXTP

2

SX

C

A

2

SX

R

A

2

SXR

L2

SXC

L2

S

XEN

2

R

eser

ved

S

X

LA

TC

H

0

SXTP

0

SX

C

A

0

SX

R

A

0

SXR

L0

SXC

L0

S

XEN

0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

*

*

*

*

*

*

*

*

*

*

*

*

*

0

*

Bits

Name

Description