Table 10-20. stuart register locations, 1 uart register differences, Table 10-20 – Intel PXA26X User Manual

Page 393

Intel® PXA26x Processor Family Developer’s Manual

10-27

Universal Asynchronous Receiver/Transmitter

10.5.1

UART Register Differences

The default descriptions for BTMCR, BTMSR and STMCR are modified as shown in

.

0x4020 0010

X

BTMCR

“Modem Control Register (MCR)”

(read/write)

0x4020 0014

X

BTLSR

(read only)

0x4020 0018

X

BTMSR

(read only)

0x4020 001C

X

BTSPR

(read/write)

0x4020 0020

X

BTISR

“Infrared Selection Register (ISR)”

(read/write)

0x4020 0000

1

BTDLL

“Divisor Latch Registers (DLL and DLH)”

low byte

(read/write)

0x4020 0004

1

BTDLH

“Divisor Latch Registers (DLL and DLH)”

(read/write)

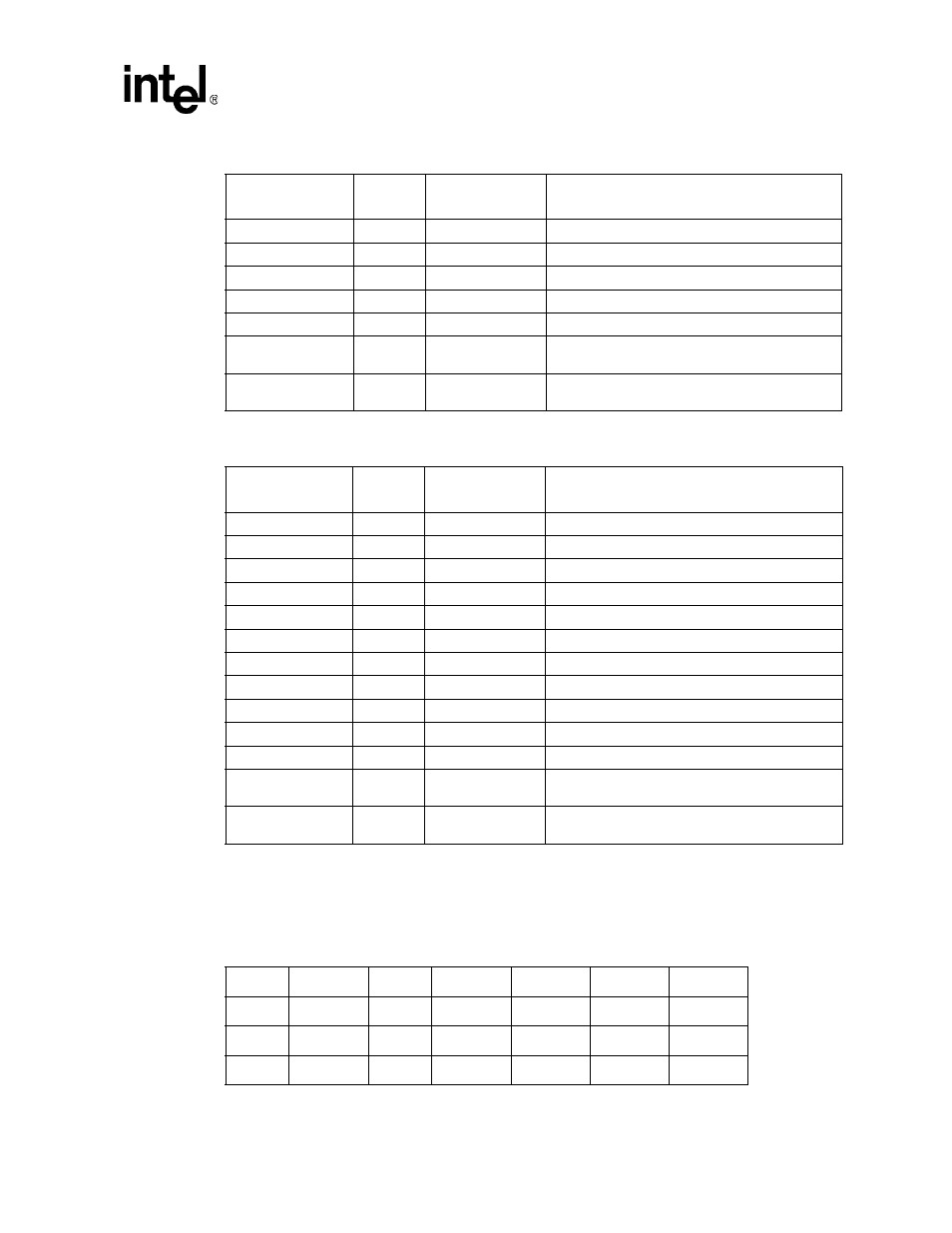

Table 10-20. STUART Register Locations

Register

Addresses

DLAB Bit

Value

Name

Description

0x4070 0000

0

STRBR

“Receive Buffer Register (RBR)”

(read only)

0x4070 0000

0

STTHR

“Transmit Holding Register (THR)”

(write only)

0x4070 0004

0

STIER

“Interrupt Enable Register (IER)”

(read/write)

0x4070 0008

X

STIIR

“Interrupt Identification Register (IIR)”

(read only)

0x4070 0008

X

STFCR

(write only)

0x4070 000C

X

STLCR

(read/write)

0x4070 0010

X

STMCR

“Modem Control Register (MCR)”

(read/write)

0x4070 0014

X

STLSR

(read only)

0x4070 0018

X

STMSR

(read only)

0x4070 001C

X

STSPR

(read/write)

0x4070 0020

X

STISR

“Infrared Selection Register (ISR)”

(read/write)

0x4070 0000

1

STDLL

“Divisor Latch Registers (DLL and DLH)”

low byte

(read/write)

0x4070 0004

1

STDLH

“Divisor Latch Registers (DLL and DLH)”

high byte

(read/write)

Table 10-19. BTUART Register Locations

Register

Addresses

DLAB Bit

Value

Name

Description

Table 10-21. Flow Control Registers in BTUART and STUART

Bit7-5

Bit4

Bit3

Bit2

Bit1

Bit0

BTMCR

Reserved

LOOP

OUT2

Reserved

RTS

Reserved

BTMSR

Reserved

CTS

Reserved

Reserved

Reserved

DCTS

STMCR

Reserved

LOOP

OUT2

Reserved

Reserved

Reserved