3 control transaction type, Table 12-9. control transaction formats, 4 interrupt transaction type – Intel PXA26X User Manual

Page 418: Table 12-10. interrupt transaction formats, 6 udc device requests

12-8

Intel® PXA26x Processor Family Developer’s Manual

Universal Serial Bus Device Controller

12.3.5.3

Control Transaction Type

The host uses control transactions to configure endpoints and query their status. Like bulk

transactions, control transactions begin with a setup packet, followed by an optional data packet,

then a handshake packet. Control transactions, by default, use DATA0 type transfers.

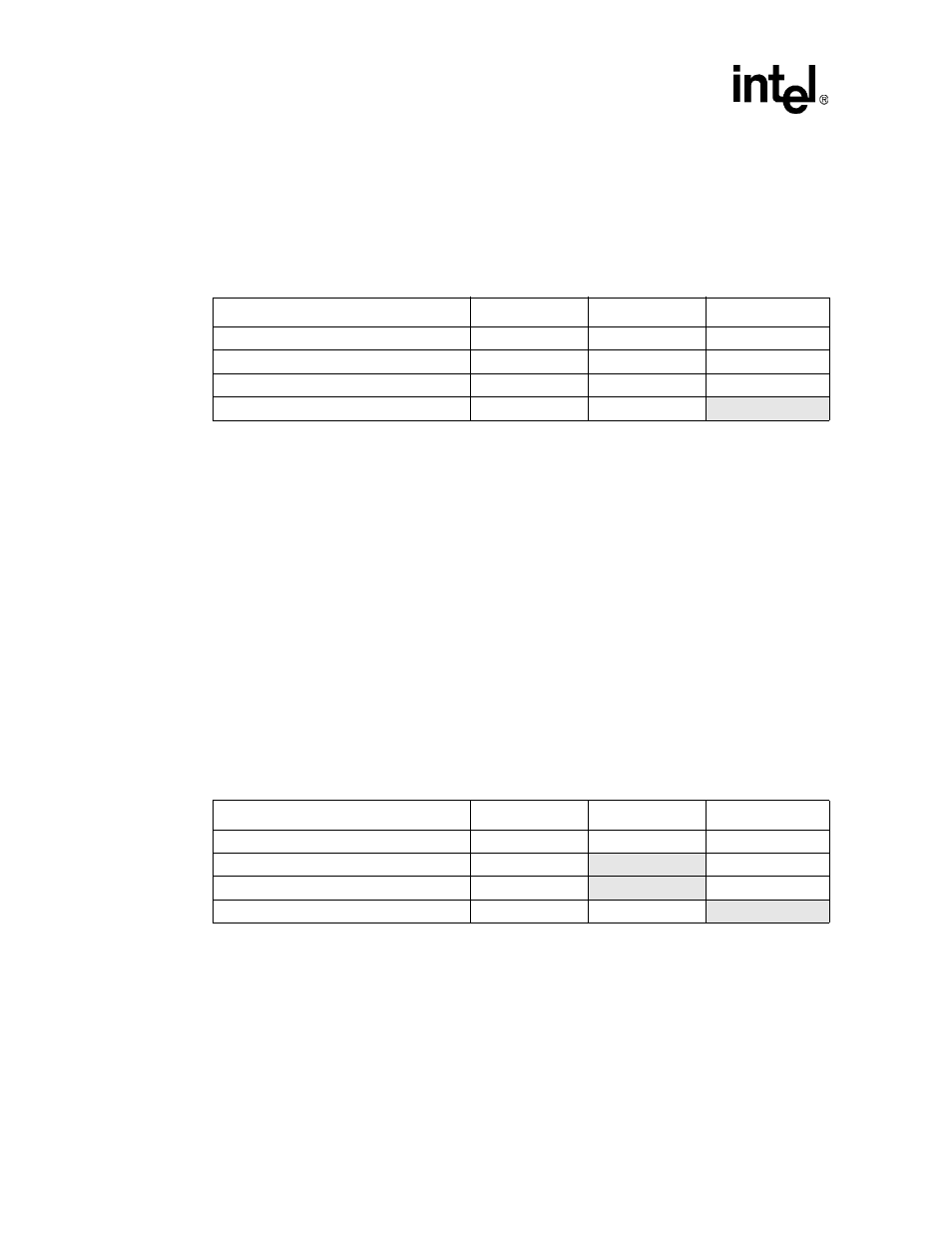

shows the four types of control transactions.

To assemble control transfers, the host sends a control transaction to tell the UDC what type of

control transfer is taking place (control read or control write), followed by one or more data

transactions. The setup is the first stage of the control transfer. The device must respond with an

ACK or no handshake (if the data is corrupted). The control transaction, by default, uses a DATA0

transfer and each subsequent data transaction toggles between DATA1 and DATA0 transfers. A

control write to an endpoint uses OUT transactions. Control reads use IN transactions. The transfer

direction is the opposite of the last data transaction. The transfer direction is used to report status

and functions as a handshake. For a control write, the last transaction is an IN from the UDC to the

host. For a control read, the last transaction is an OUT from the host to the UDC. The last data

transaction always uses a DATA1 transfer, even if the previous transaction used DATA1.

12.3.5.4

Interrupt Transaction Type

The host uses interrupt transactions to query the status of the device. Like bulk transactions,

interrupt transactions begin with a setup packet, followed by an optional data packet, then a

handshake packet. Interrupt transactions, by default, use DATA0 type transfers.

shows the four types of interrupt transactions.

12.3.6

UDC Device Requests

The UDC uses its control, status, and data registers to control and monitor the transmit and receive

FIFOs for endpoints 1 - 15. The host controls all other UDC configuration and status reporting

using device requests that are sent as control transactions to endpoint 0 via the USB. Each setup

packet to endpoint 0 is 8 bytes long and specifies:

Table 12-9. Control Transaction Formats

Action

Token Packet

Data Packet

Handshake Packet

UDC successfully received control from host

SETUP

DATA0

ACK

UDC temporarily unable to receive data

SETUP

DATA0

NAK

UDC endpoint needs host intervention

SETUP

DATA0

STALL

UDC detected PID, CRC, or bit stuff error

SETUP

DATA0

None

NOTE: Packets from UDC to host are boldface

Table 12-10. Interrupt Transaction Formats

Action

Token Packet

Data Packet

Handshake Packet

Host successfully received data from UDC

IN

DATA0

ACK

UDC temporarily unable to transmit data

IN

None

NAK

UDC endpoint needs host intervention

IN

None

STALL

Host detected PID, CRC, or bit stuff error

IN

DATA0

None

NOTE: Packets from UDC to host are boldface