Intel PXA26X User Manual

Page 289

Intel® PXA26x Processor Family Developer’s Manual

7-21

Liquid Crystal Display Controller

19:12

PDD

PALETTE DMA REQUEST DELAY (

Value (0–255) specifies the number of internal bus clocks before requesting another palette

data burst. The counter starts decrementing when the first word is written to the input FIFO

buffer. PDD = 0x00 disables this function.

11

QDM

LCD QUICK DISABLE MASK (

0 – Generate an interrupt after quick disable.

1 – Quick Disable (QD) status does not generate an interrupt.

10

DIS

LCD DISABLE (

):

0 – LCD controller has not been disabled.

1 – LCD controller has been disabled, or is in the process of disabling.

9

DPD

DOUBLE-PIXEL DATA (DPD) PIN MODE (

In passive monochrome single panel mode,

0 – L_DD[3:0] pins are used to send 4 pixel values each pixel clock transition.

1 – L_DD[7:0] pins are used to send 8 pixel values each pixel clock.

In any other mode, DPD must be 0.

8

—

Reserved.

7

PAS

PASSIVE/ACTIVE DISPLAY SELECT (

0 – Passive (or STN) display operation enabled.

1 – Active (or TFT) display operation enabled.

6

EFM

END OF FRAME MASK (

):

0 – Generates an interrupt at the end of a frame.

1 – End of frame (EOF) condition does not generate an interrupt.

5

IUM

INPUT FIFO UNDERRUN MASK (

0 – FIFO underrun errors generate an interrupt.

1 – FIFO underrun errors do not generate an interrupt.

4

SFM

START OF FRAME MASK (

):

0 – Starting a new frame (after loading frame descriptor) generates an interrupt.

1 – Start of frame (SOF) condition does not generate an interrupt.

3

LDM

LCD DISABLE DONE MASK (

):

0 – LCD disable done condition generates an interrupt (state of LDD status sent to the

interrupt controller).

1 – LCD disable done condition does not generate an interrupt (LDD status bit ignored).

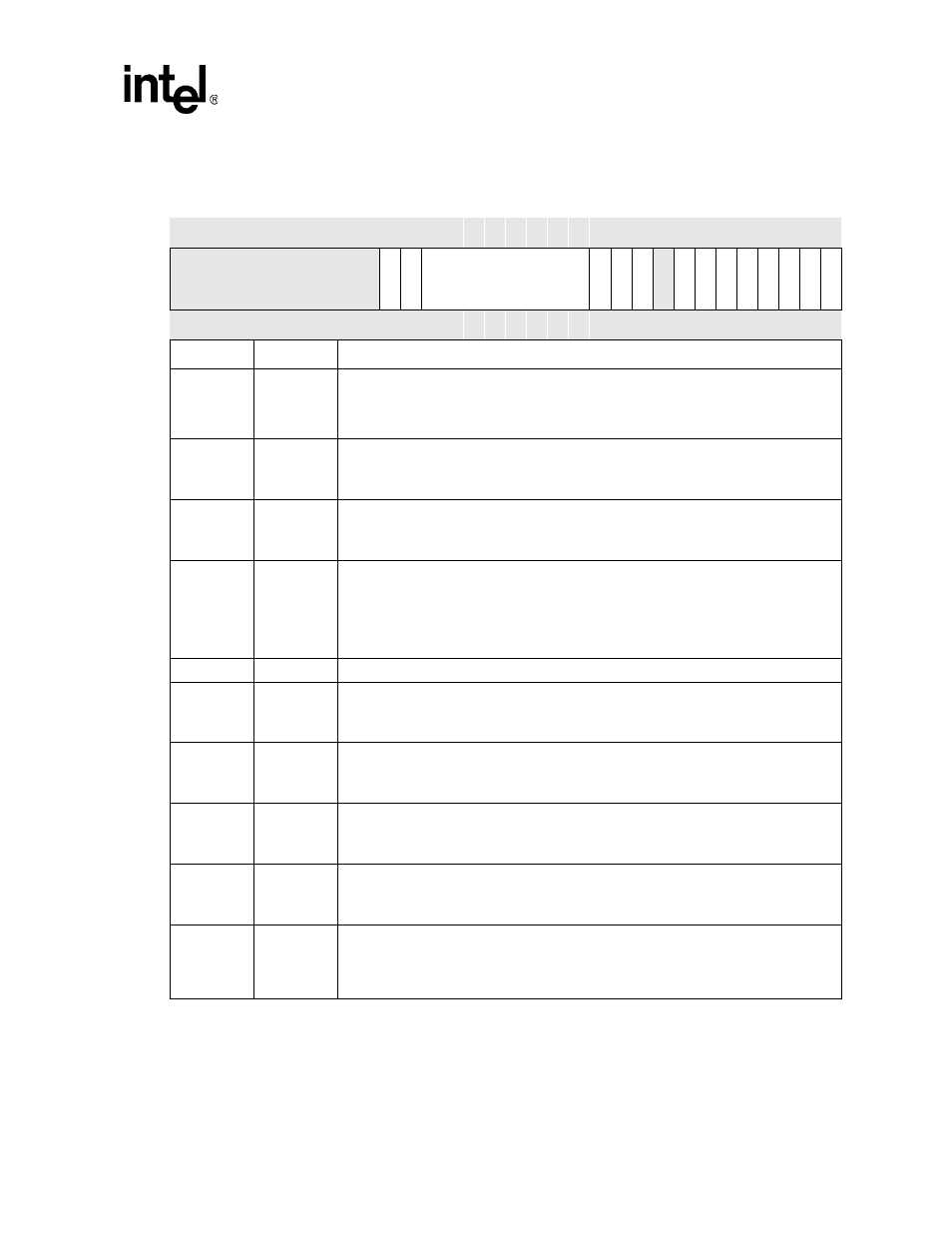

Table 7-2. LCD Controller Control Register 0 (Sheet 2 of 3)

Physical Address

0x4400_0000

LCD Controller Control Register 0

LCD Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

R

eser

ved

OU

M

BM

PDD

QD

M

DI

S

DP

D

R

eser

ved

PA

S

EFM

IU

M

SFM

LD

M

SD

S

CM

S

EN

B

Reset

X

X

X

X

X

X

X

X

X

X

X

X

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description