7 reset, 8 internal registers – Intel PXA26X User Manual

Page 37

Intel® PXA26x Processor Family Developer’s Manual

2-7

System Architecture

Note:

Clearing interrupts may take a delay. To allow the status bit to clear before returning from an

interrupt service routine (ISR), clear the interrupt early in the routine.

2.7

Reset

shows each pin’s state after each type of reset.

2.8

Internal Registers

All internal registers are mapped in physical memory space on 32-bit address boundaries. Use

word access loads and stores to access internal registers. Internal register space must be mapped as

non-cacheable.

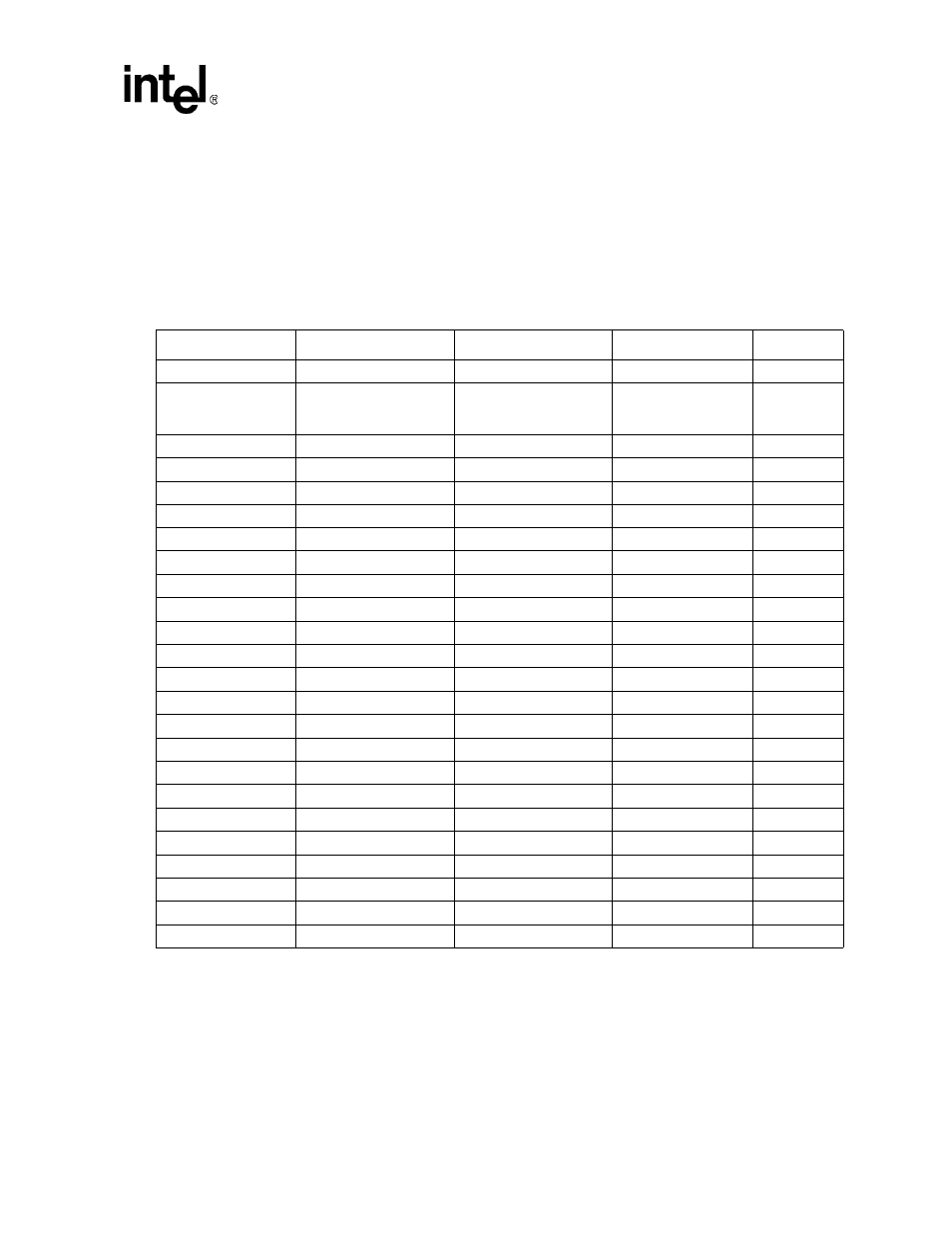

Table 2-4. Effect of Each Type of Reset on Internal Register State

Unit

Sleep Mode

GPIO Reset

Watchdog Reset

Hard Reset

Core

reset

reset

reset

reset

Memory Controller

reset

All registers except

configuration registers

(refresh maintained)

reset

reset

LCD Controller

reset

reset

reset

reset

DMA Controller

reset

reset

reset

reset

Full Function UART

reset

reset

reset

reset

Bluetooth UART

reset

reset

reset

reset

Standard UART

reset

reset

reset

reset

Hardware UART

reset

reset

reset

reset

I

2

C

reset

reset

reset

reset

I

2

S

reset

reset

reset

reset

AC97

reset

reset

reset

reset

USB

reset

reset

reset

reset

ICP

reset

reset

reset

reset

RTC

preserved

preserved

reset (except RTTR)

reset

OS Timer

reset

reset

reset

reset

PWM

reset

reset

reset

reset

Interrupt Controller

reset

reset

reset

reset

GPIO

reset

reset

reset

reset

Power Manager

preserved

reset

reset

reset

SSP

reset

reset

reset

reset

Network SSP

reset

reset

reset

reset

Audio SSP

reset

reset

reset

reset

MMC

reset

reset

reset

reset

Clocks

preserved (except CP14)

preserved (except CP14)

reset (except OSCC)

reset