4 memory accesses – Intel PXA26X User Manual

Page 196

6-6

Intel® PXA26x Processor Family Developer’s Manual

Memory Controller

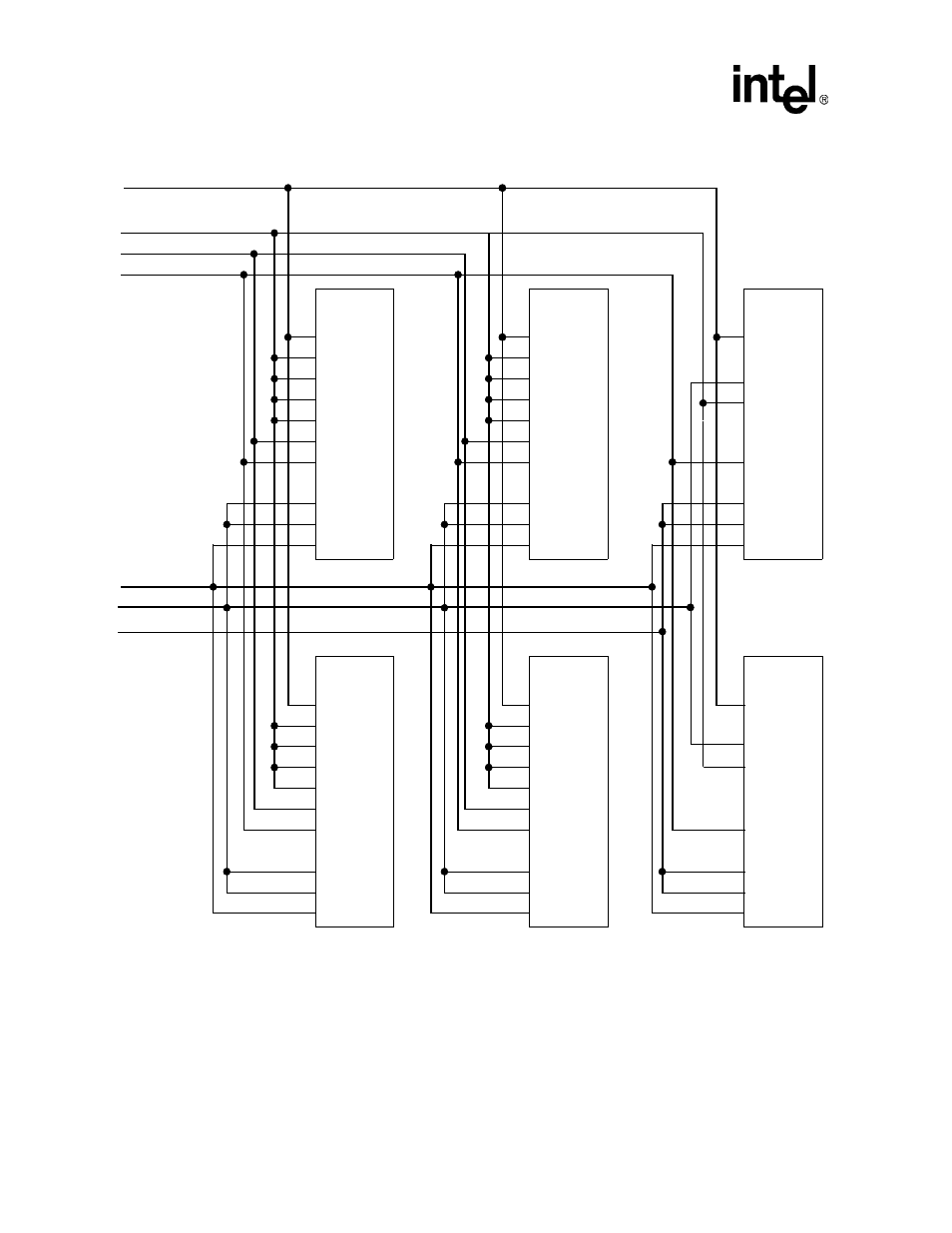

Figure 6-3. Asynchronous Static Memory System Example

6.4

Memory Accesses

If a memory access is followed by an idle bus period, the control signals return to their inactive

state. The address and data signals remain at their previous values to avoid unnecessary bus

transitions and eliminate the need for multiple pull-up resistors.

2Mx16

SMROM

nCS

nRAS

nCAS

CLK

CKE

nMR

addr(12:0)

DQML

DQMH

DQ(15:0)

2Mx16

SMROM

nCS

nRAS

nCAS

CLK

CKE

nMR

addr(12:0)

DQML

DQMH

DQ(15:0)

SRAM

nCS

nOE

nWE

addr(20:0)

DQML

DQMH

DQ(15:0)

2Mx16

SMROM

nCS

nRAS

nCAS

CLK

CKE

nMR

addr(12:0)

DQML

DQMH

DQ(15:0)

2Mx16

SMROM

nCS

nRAS

nCAS

CLK

CKE

nMR

addr(12:0)

DQML

DQMH

DQ(15:0)

SRAM

nCS

nOE

nWE

addr(20:0)

DQML

DQMH

DQ(15:0)

MD(31:0)

nOE

MA(22:2)

SDCLK(0)

nSDRAS, nSDCAS, nWE, CKE(0)

nCS(2:0)

0

0

1

1

2

2

15:0

31:16

DQM[3:0]

31:16

31:16

3

2

1

0

15:0

15:0

22:10

22:10

22:10

22:10

22:2

22:2

0

0

1

1

2

2

3

3