Intel PXA26X User Manual

Page 570

16-22

Intel® PXA26x Processor Family Developer’s Manual

Network/Audio Synchronous Serial Protocol Serial Ports

29

R/W

EBCEI

BIT COUNT ERROR INTERRUPT MASK:

Disables bit count error interrupts. SSSR will still indicate an error. A bit

count error occurs when the SSP is a slave to clock or frame and the

SSP detects a new frame before the internal bit counter has reached 0.

0 – Bit count error events will generate an interrupt.

1 – Bit count error events will not generate an interrupt.

28

R/W

SCFR

SLAVE CLOCK FREE RUNNING:

SCFR in slave mode (SCLKDIR set) must be cleared if the input clock

from the external source is running continuously.

In master mode (SCLKDIR cleared) this bit is ignored.

Master mode only:

0 – Clock input to SSPSCLK is continuously running

1 – Clock input to SSPSCLK is active only during transfers.

27:26

—

—

Reserved

25

R/W

SCLKDIR

SSP PORT SERIAL BIT RATE CLOCK DIRECTION:

Determines whether the port is the master or slave (with respect to

driving SSPSCLK).

0 – Master mode, the port generates SSPSCLK internally, acts as the

master, and drives SSPSCLK.

1 – Slave mode, the port acts as a slave, receives SSPSCLK from an

external device and uses it to determine when to drive transmit

data on SSPTXD and when to sample Receive data on SSPRXD.

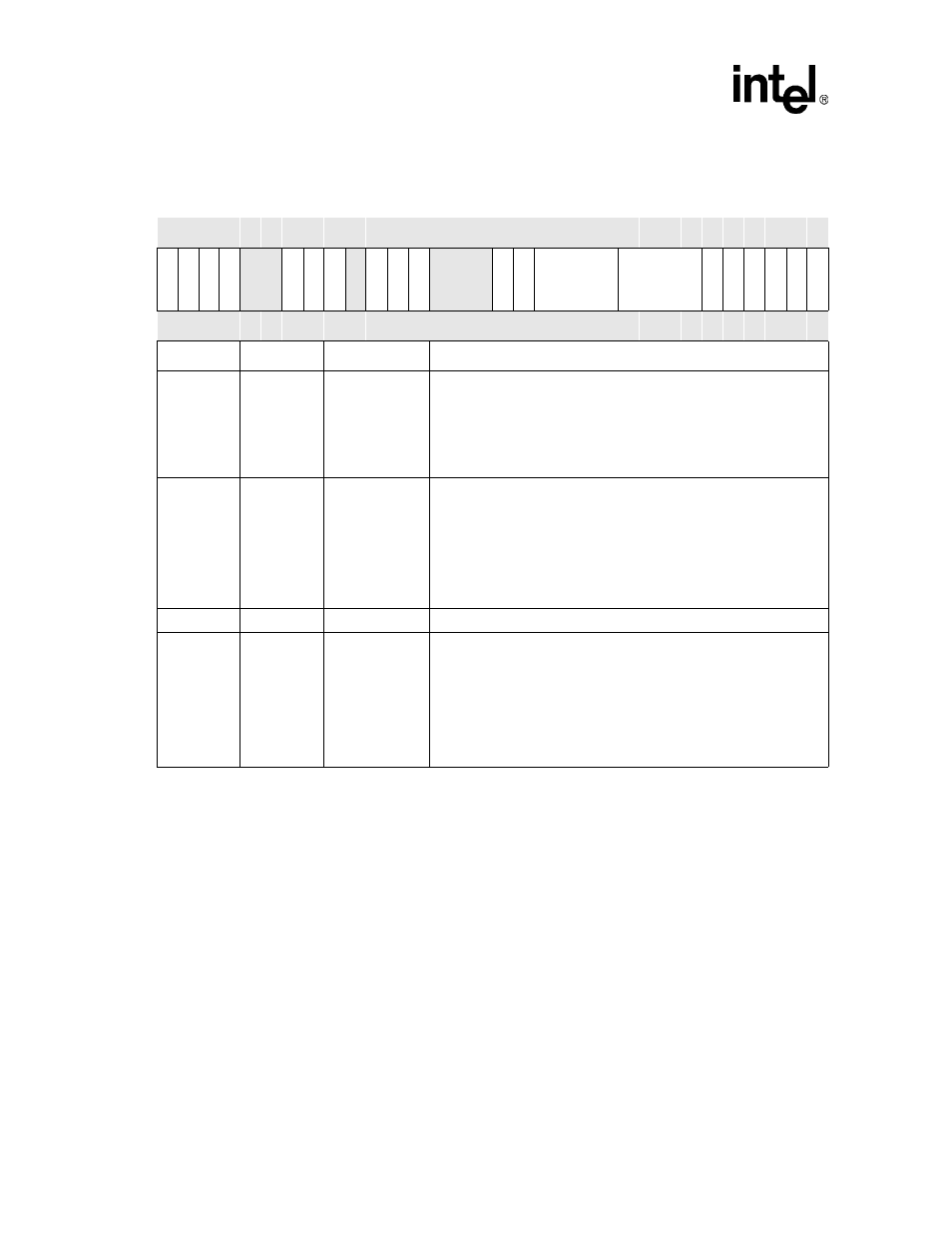

Table 16-4.

SSCR1 Bit Definitions (Sheet 2 of 6)

Physical Address

Base+0x04

SSCR1

PXA26x processor family Network/Audio

SSP Serial Ports

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

TTELP

TTE

EB

CEI

SC

F

R

Re

s

e

rv

e

d

SC

L

K

D

IR

S

F

RM

DI

R

RW

O

T

Re

s

e

rv

e

d

TS

R

E

RS

R

E

TIN

T

E

Re

s

e

rv

e

d

STRF

EFW

R

RFT

TFT

MW

D

S

SPH

SP

O

LB

M

TIE

RI

E

Reset

0

0

0

0

?

?

0

0

0

0

0

0

0

?

?

?

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Access

Name

Description