6 fifo control register (fcr) – Intel PXA26X User Manual

Page 378

10-12

Intel® PXA26x Processor Family Developer’s Manual

Universal Asynchronous Receiver/Transmitter

10.4.2.6

FIFO Control Register (FCR)

The FCR is a write-only register that is located at the same address as the IIR, which is a read-only

register. The FCR enables/disables the transmitter/receiver FIFOs, clears the transmitter/receiver

FIFOs, and sets the receiver FIFO trigger level.

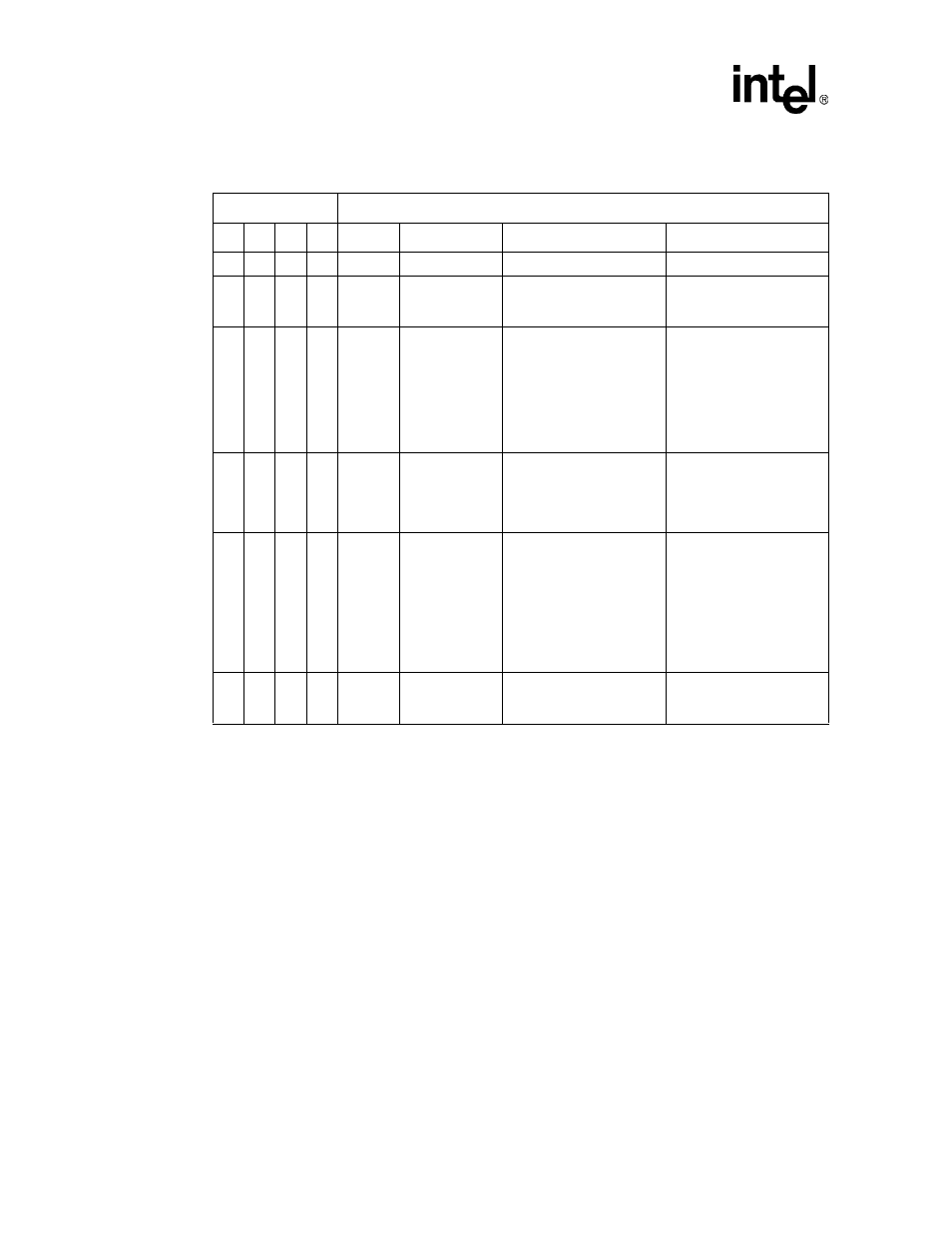

Table 10-10. Interrupt Identification Register Decode

Interrupt ID Bits

Interrupt SET/RESET Function

3

2

1

0

Priority

Type

Source

Cleared By...

0

0

0

1

—

None

No interrupt is pending

—

0

1

1

0

Highest

Receiver Line

Status

Overrun error, parity error,

framing error, break

interrupt

Reading the LSR

0

1

0

0

Second

Highest

Received Data

Available

Non-FIFO mode: Receive

buffer is full

FIFO mode: Trigger level

was reached

Non-FIFO mode: Reading

the Receiver Buffer

Register

FIFO mode: Reading bytes

until receiver FIFO drops

below trigger level or setting

FCR[RESETRF].

1

1

0

0

Second

Highest

Character

Timeout

Indication

FIFO mode only: At least

one character is in the

receive FIFO and no data

has been sent for four

character times.

Reading the receiver FIFO,

setting FCR[RESETRF] or

a new start bit is received

0

0

1

0

Third

Highest

Transmit FIFO

Data Request

Non-FIFO mode: Transmit

Holding Register empty

FIFO mode: Transmit has

half, or less than half, data

Non-FIFO mode: Reading

the IIR (if the source of the

interrupt) or writing into the

Transmit Holding Register

FIFO mode: Reading the

IIR Register (if the source of

the interrupt) or writing to

the transmitter FIFO

0

0

0

0

Fourth

Highest

Modem Status

Clear to send, data set

ready, ring indicator, data

carrier detect

Reading the Modem Status

Register