Intel PXA26X User Manual

Page 483

Intel® PXA26x Processor Family Developer’s Manual

13-21

AC97 Controller Unit

7:6

—

Reserved

5

SECRES_IEN

SECONDARY RESUME INTERRUPT ENABLE:

0 – Interrupt is disabled

1 – Enables an interrupt to occur when the secondary codec causes a resume event on

the AC-link

4

PRIRES_IEN

PRIMARY RESUME INTERRUPT ENABLE:

0 – Interrupt is disabled

1 – Enables an interrupt to occur when the primary codec causes a resume event on the

AC-link

3

ACLINK_OFF

AC-LINK SHUT OFF:

0 – If the AC-link was off, turns it back on, otherwise this bit has no effect.

1 – Causes the controller to drive SDATA_OUT and SYNC outputs low and turn off input

buffer enables. The reset output is however maintained high. The AC-link is allowed to

access any of the FIFOs.

Setting this bit does not ensure a clean shut down. Software must make sure that all

transactions are complete before setting this bit.

2

WARM_RST

AC97 WARM RESET:

0 – A warm reset is not generated.

1 – Causes a warm reset to occur on the AC-link. The warm reset awakens a suspended

codec without clearing it’s internal registers.

If software attempts to perform a warm reset while BITCLK is running, the write will be

ignored and the bit will not change. This bit is self clearing i.e., it remains set until the reset

completes and BITCLK is seen on the AC-link after which it clears itself.

1

COLD_RST

AC'97 COLD RESET:

0 – Causes a cold reset to occur throughout the AC'97 circuitry. All data in the Controller

and the codec is lost.

1 – A cold reset is not generated.

Defaults to a 0 and after reset, the driver must to set this bit to a 1.The value of this bit is

retained after suspends, hence, if this bit was set to a 1 before a suspend, a cold reset is not

generated on a resume.

0

GIE

CODEC GPI INTERRUPT ENABLE (GIE):

This bit controls whether the change in status of any modem codec GPI causes an interrupt.

0 – If this bit is not set, bit 0 of the Global Status Register is set, but an interrupt is not

generated.

1 – If this bit is set the change in value of a GPI (as indicated by bit 0 of slot 12) causes an

interrupt and sets bit 0 of the Global Status Register

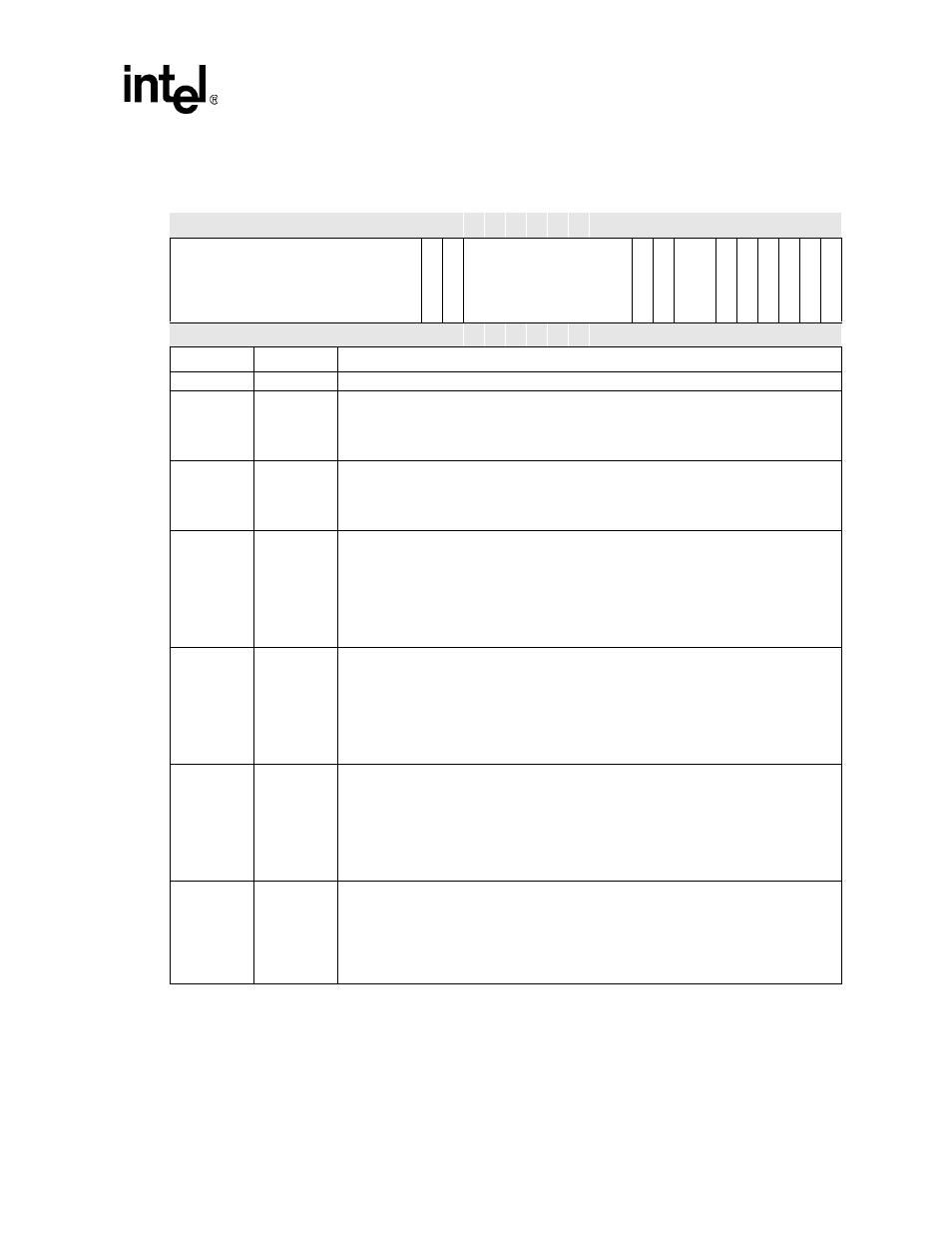

Table 13-8. Global Control Register (Sheet 2 of 2)

Physical Address

4050_000C

GCR Register

AC97

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Reserved

CD

ON

E_

IE

SD

O

N

E_

IE

Reserved

SEC

RD

Y_

IEN

PR

IR

DY

_

IE

N

R

eser

ved

SEC

RE

S_

IEN

P

R

IR

ES_IEN

AC

L

INK

_

O

F

F

WA

R

M

_

R

S

T

CO

L

D

_

R

ST

GI

E

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description