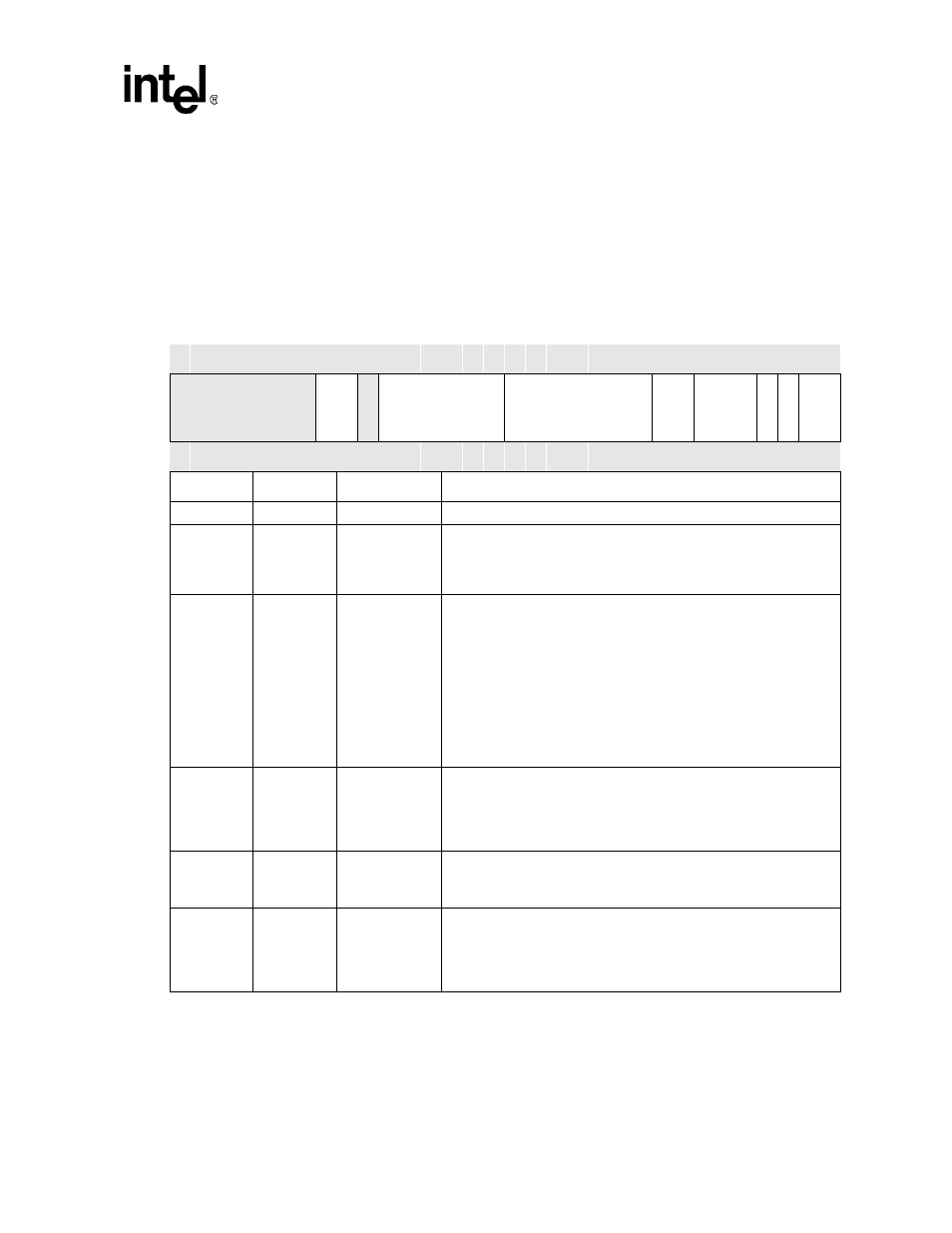

Table 16-5. sspsp bit definitions (sheet 1 of 2), Section 16.5.3 – Intel PXA26X User Manual

Page 575

Intel® PXA26x Processor Family Developer’s Manual

16-27

Network/Audio Synchronous Serial Protocol Serial Ports

16.5.3

SSP Programmable Serial Protocol Register (SSPSP)

, contains bit fields used to program the various programmable serial-

protocol parameters. The contents of these registers are ignored if the PSP is not selected.

These are read/write registers. Ignore reads from reserved bits. Write zeros to reserved bits.

Table 16-5. SSPSP Bit Definitions (Sheet 1 of 2)

Physical Address

Base + 0x2C

SSPSP

PXA26x processor family Network/Audio

SSP Serial Ports

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Reserved

DM

YS

T

O

P

R

eser

ved

SFRMWDTH

SFRMDLY

DM

Y

S

T

R

T

ST

RTD

L

Y

ETD

S

SF

R

M

P

SCM

O

DE

Reset

?

?

?

?

?

?

?

0

0

?

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Access

Name

Description

31:25

—

—

Reserved

24:23

R/W

DMYSTOP

DUMMY STOP:

Determines the number of serial clock (SSPSCLK) cycles that

SSPSCLK is active following the last bit (bit 0) of transmitted (SSPTXD)

or received data (SSPRXD).

22:16

R/W

SFRMWDTH

SERIAL FRAME WIDTH:

Determines the number of serial clock periods of the frame width

(SSPSFRM active).

The programmed value must not be greater than:

(Start Delay)

max

+ (Dummy start)

max

+ (Data size)

max

+ (Dummy Stop)

max

.

In slave mode (SSCR1[SFRMDIR] set), this field is ignored, however

the incoming frame signal must be asserted for at least 1 SSPSCLK

duration.

In PSP mode, the incoming frame signal must be deasserted for at least

1 SSPSCLK after assertion (before the next sample is transferred).

15:9

R/W

SFRMDLY

SERIAL FRAME DELAY:

Determines the number of half serial clock periods that SSPSFRM is

delayed from the start of the transfer. The programed value sets the

number of half SSPSCLK cycles from the time TXD/RXD starts being

driven to the time SSPSFRM is asserted, from 0 to 74.

8:7

R/W

DMYSTRT

DUMMY START:

Determines the number of SSPSCLK cycles after STRTDLY that

precede the transmitted (SSPTXD) or received data (SSPRXD).

6:4

R/W

STRTDLY

THREE-BIT START DELAY FIELD:

Determines the number of SSPSCLK cycles that SSPSCLK remains in

its Idle state between data transfers. The start delay field must be

programmed to 0 whenever SSPSCLK or SSPSFRM is configured as

an input (SSCR1[SCLKDIR] = 1 or SSCR1[SFRMDIR] = 1).