3 mmc_clkrt register – Intel PXA26X User Manual

Page 535

Intel® PXA26x Processor Family Developer’s Manual

15-23

MultiMediaCard Controller

15.5.3

MMC_CLKRT Register

The MMC_CLKRT register specifies the frequency division of the MMC bus clock. The software

is responsible for setting this register.

8

CLK_EN

CLOCK ENABLED:

0 – MMC clock is off

1 – MMC clock is on

7

RECV_FIFO_

FULL

RECEIVE FIFO FULL:

0 – Receive FIFO is not full

1 – Receive FIFO is full

6

XMIT_FIFO_E

MPTY

TRANSMIT FIFO EMPTY:

0 – Transmit FIFO is not empty

1 – Transmit FIFO is empty

5

RES_CRC_E

RR

RESPONSE CRC ERROR:

0 – No error on the response CRC

1 – CRC error occurred on the response

4

SPI_READ_E

RROR_TOKE

N

SPI READ ERROR TOKEN:

0 – SPI data error token has not been received

1 – SPI data error token has been received

3

CRC_READ_

ERROR

CRC READ ERROR:

0 – No error on received data

1 – CRC error occurred on received data

2

CRC_WRITE_

ERROR

CRC WRITE ERROR:

0 – No error on transmission of data

1 – Card observed erroneous transmission of data

1

TIME_OUT_R

ESPONSE

TIME OUT RESPONSE:

0 – Card response has not timed out

1 – Card response timed out

0

READ_TIME_

OUT

READ TIME OUT:

0 – Card read data has not timed out

1 – Card read data timed out

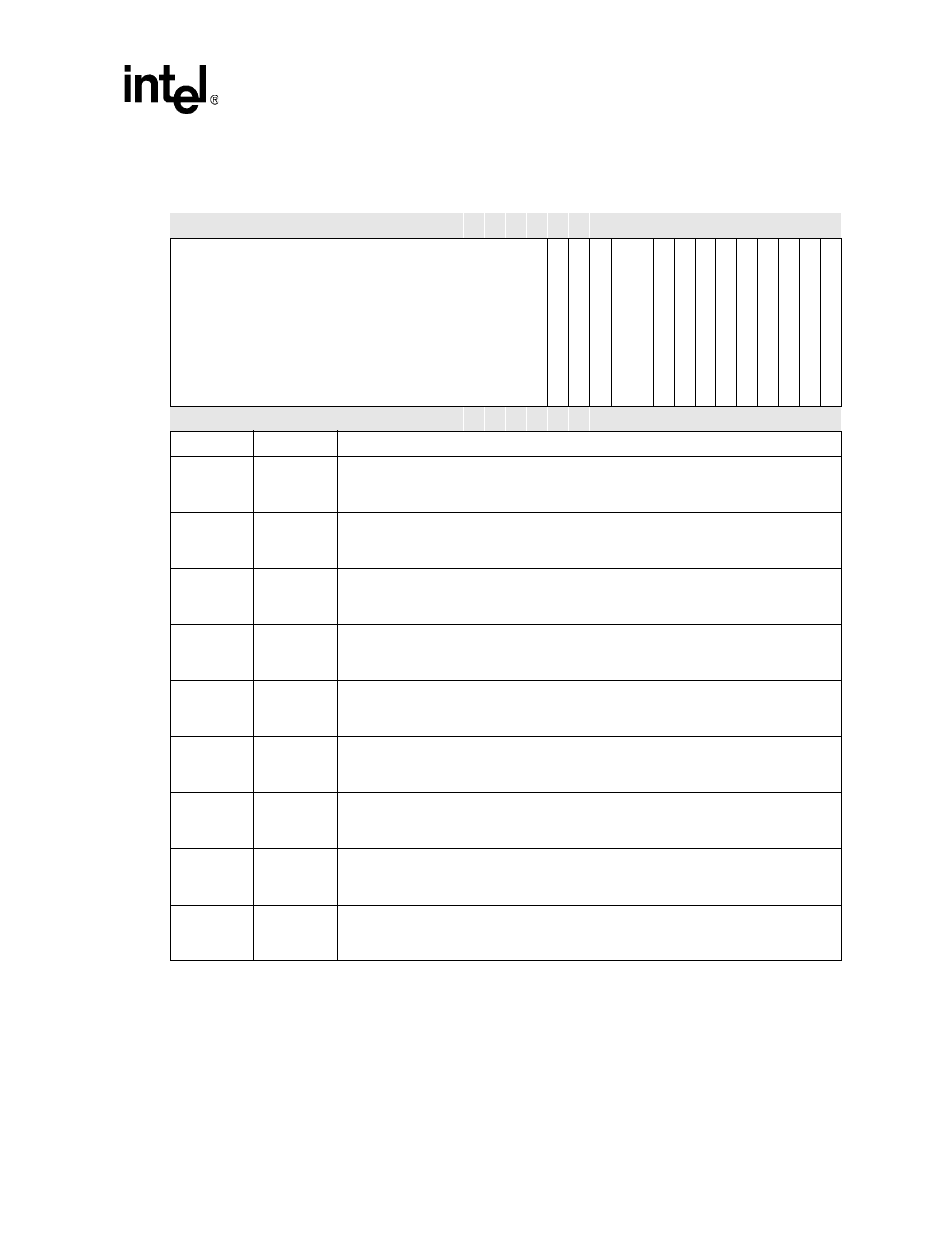

Table 15-7. MMC_STAT Register (Sheet 2 of 2)

Physical Address

4110_0004

MMC_STAT Register

MMC

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

R

eser

ved

E

N

D

_

CM

D_

R

E

S

PR

G

_

D

O

N

E

DA

T

A

_

T

RA

N_

DO

N

E

R

eser

ved

CL

K

_

EN

RE

CV

_

F

IF

O_

F

U

L

L

XM

IT_FIFO

_

E

M

PTY

RES

_

CR

C_

ER

R

S

P

I_

R

E

AD

_

E

RR

OR_

T

OK

E

N

CR

C_

R

E

AD

_

E

RR

O

R

CR

C_

W

R

IT

E

_

ER

RO

R

TIM

E

_O

U

T

_R

E

S

P

O

N

S

E

RE

AD

_

T

IM

E

_

OU

T

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

Bits

Name

Description