Intel PXA26X User Manual

Page 485

Intel® PXA26x Processor Family Developer’s Manual

13-23

AC97 Controller Unit

7

MINT

MIC IN INTERRUPT (MINT):

0 – None of the Mic-in channel interrupts occurred.

1 – One of the Mic-in channel interrupts occurred.

When the specific interrupt is cleared, this bit will be cleared (interruptible).

6

POINT

PCM OUT INTERRUPT (POINT):

0 – None of the PCM out channel interrupts occurred.

1 – One of the PCM out channel interrupts occurred.

When the specific interrupt is cleared, this bit will be cleared (interruptible).

5

PIINT

PCM IN INTERRUPT (PIINT):

0 – None of the PCM in channel interrupts occurred.

1 – One of the PCM in channel interrupts occurred.

When the specific interrupt is cleared, this bit will be cleared (interruptible).

4:3

—

Reserved

2

MOINT

MODEM OUT INTERRUPT (MOINT):

0 – None of the Modem out channel interrupts occurred.

1 – One of the Modem out channel interrupts occurred.

When the specific interrupt is cleared, this bit will be cleared (interruptible).

1

MIINT

MODEM IN INTERRUPT (MIINT):

0 – None of the Modem in channel interrupts occurred.

1 – One of the Modem in channel interrupts occurred.

When the specific interrupt is cleared, this bit will be cleared (interruptible).

0

GSCI

CODEC GPI STATUS CHANGE INTERRUPT (GSCI):

0 – Bit 0 of slot 12 is clear.

1 – Bit 0 of slot 12 is set. This indicates that one of the GPI’s changed state and that the

new values are available in slot 12.

The bit is cleared by software writing a “1” to this bit location (interruptible).

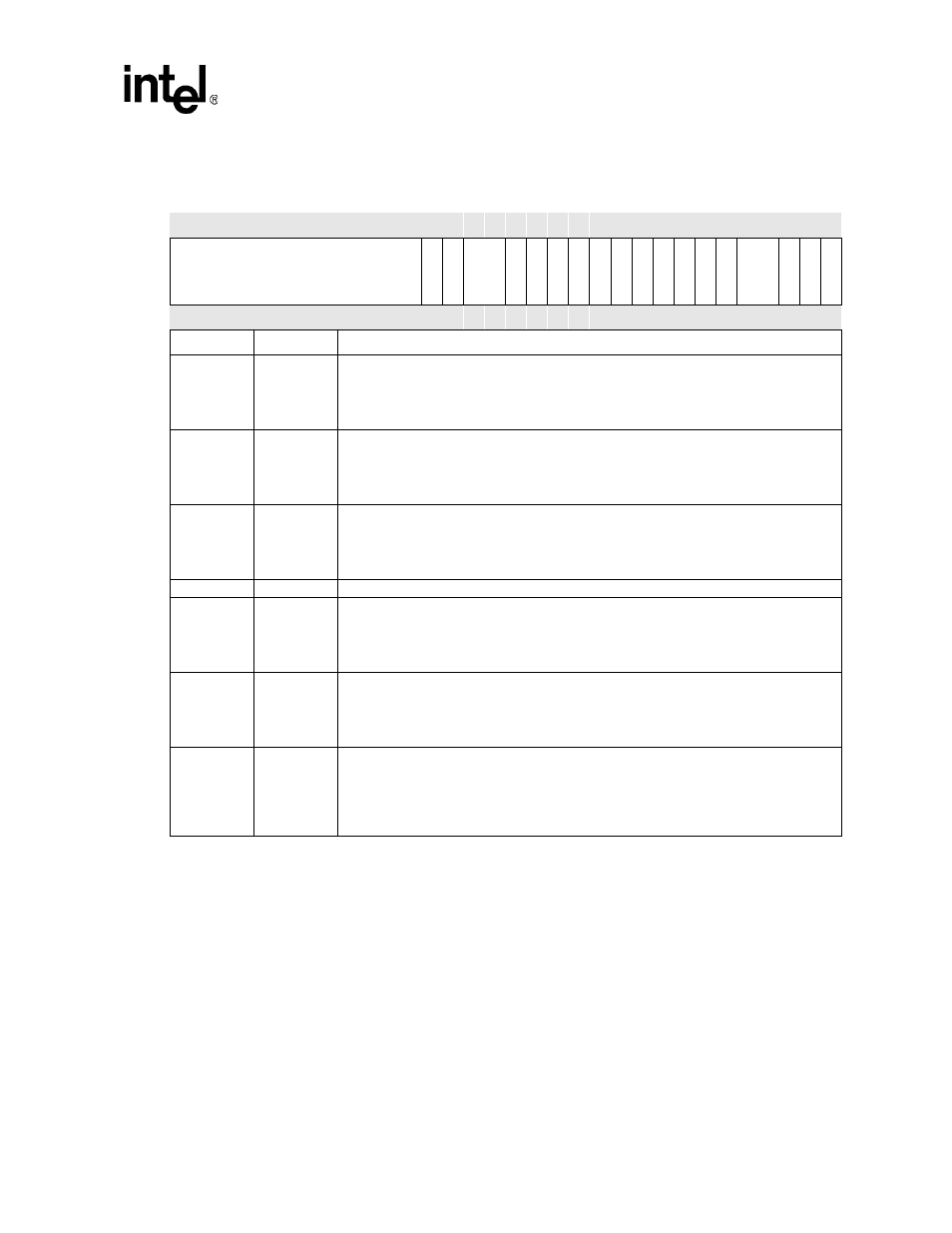

Table 13-9. Global Status Register (Sheet 2 of 2)

Physical Address

4050_001C

GSR Register

AC97

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Reserved

CDO

N

E

SDO

N

E

R

eser

v

e

d

RD

CS

B

IT3SL

T12

B

IT2SL

T12

B

IT1SL

T12

SEC

RES

PR

IR

ES

SC

R

PC

R

MI

N

T

PO

IN

T

P

IIN

T

R

eser

v

e

d

MOI

N

T

M

IIN

T

GS

CI

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description