4 tmed frame number adjuster enable (fname), 5 tmed color offset adjuster enable (coae), 6 tmed frame number adjuster matrix (fnam) – Intel PXA26X User Manual

Page 317: 7 tmed color offset adjuster matrix (coam), 11 lcd controller register summary

Intel® PXA26x Processor Family Developer’s Manual

7-49

Liquid Crystal Display Controller

7.6.10.4

TMED Frame Number Adjuster Enable (FNAME)

The frame number adjuster enable bit allows the frame number adjuster to add an offset to the

current frame number before the value is sent through the algorithm. Setting this bit enables the

addition of the current frame number to a value composed from the row and column counters. This

value comes from one of the two look up matrices which is selected by TMED[FNAM].

7.6.10.5

TMED Color Offset Adjuster Enable (COAE)

COAE enables the color offset adjuster for each color. The color offset adjuster creates the offset in

the lower boundary in the TMED algorithm (refer to

Section 7.3.3, “Temporal Modulated Energy

Distribution (TMED) Dithering” on page 7-6

). The offset is created by adding either the output of

the lookup matrix (input was the color value) or‘00’ to the seed value in the TSR for that color. The

color offset adjuster for each color can be disabled by clearing this bit. When cleared, this bit

allows only the seed register value to go through the algorithm.

7.6.10.6

TMED Frame Number Adjuster Matrix (FNAM)

FNAM selects which matrix is used with the frame number adjuster. A 1 selects the (suggested)

TMED2 matrix, and a 0 selects the older TMED matrix.

7.6.10.7

TMED Color Offset Adjuster Matrix (COAM)

COAM selects which matrix is used when using the color offset adjuster. A 1 selects the

(suggested) TMED2 matrix, and a 0 selects the older TMED matrix.

7.6.11

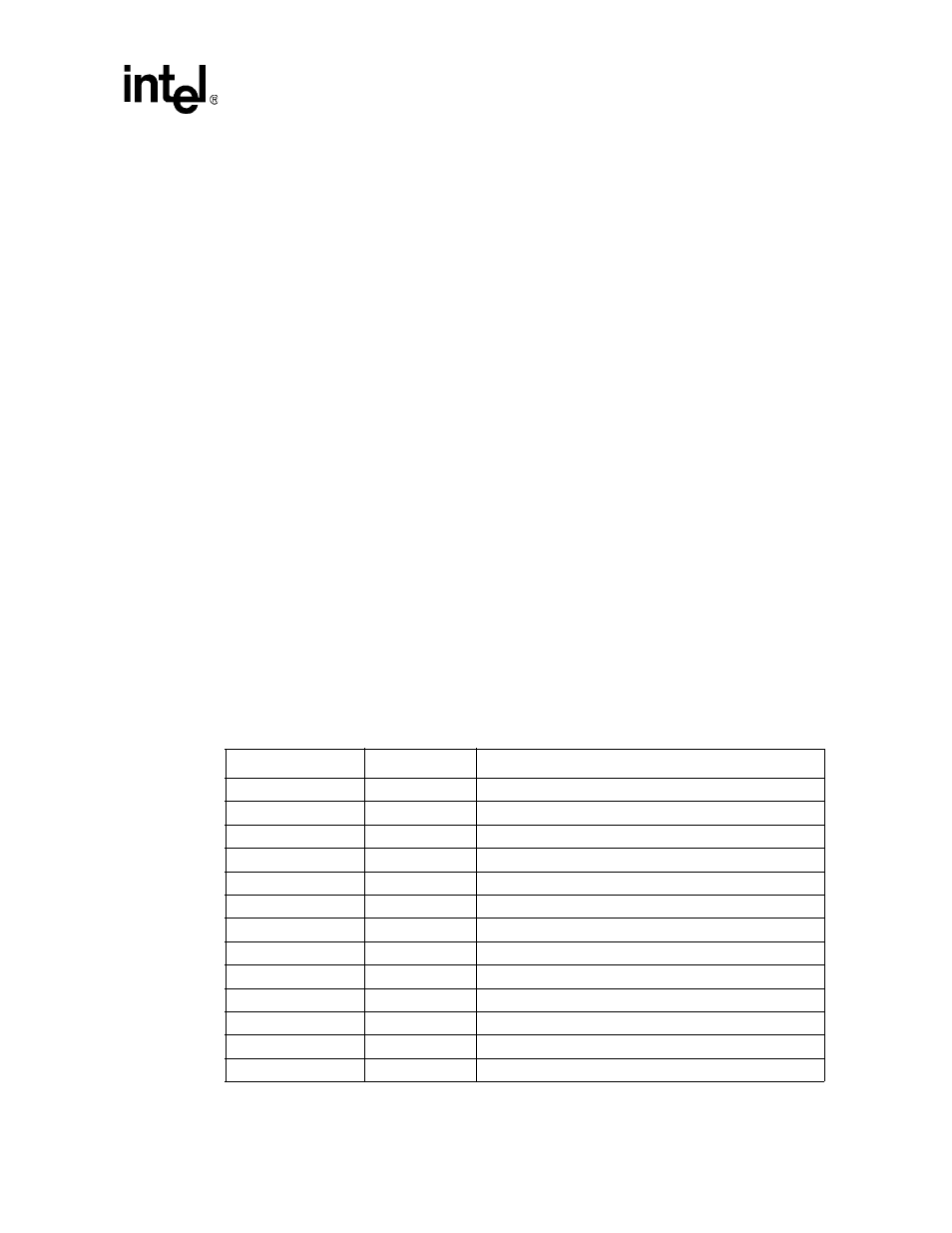

LCD Controller Register Summary

shows the registers associated with the LCD controller and their physical addresses.

Access all LCD registers as 32-bit values.

Table 7-16. LCD Controller Register Locations (Sheet 1 of 2)

Address

Name

Description

0x4400 0000

LCCR0

LCD controller control register 0

0x4400 0004

LCCR1

LCD controller control register 1

0x4400 0008

LCCR2

LCD controller control register 2

0x4400 000C

LCCR3

LCD controller control register 3

0x4400 0020

FBR0

DMA channel 0 frame branch register

0x4400 0024

FBR1

DMA channel 1 frame branch register

0x4400 0038

LCSR

LCD controller status register

0x4400 003C

LIIDR

LCD controller interrupt ID register

0x4400 0040

TRGBR

TMED RGB Seed Register

0x4400 0044

TCR

TMED Control Register

0x4400 0200

FDADR0

DMA channel 0 frame descriptor address register

0x4400 0204

FSADR0

DMA channel 0 frame source address register

0x4400 0208

FIDR0

DMA channel 0 frame ID register