Intel PXA26X User Manual

Page 34

2-4

Intel® PXA26x Processor Family Developer’s Manual

System Architecture

2.3.3

Coprocessor 14 Register 6 and 7– Clock and Power

Management

These registers allow software to use the clocking and power management modes. The valid

operations are described in

Table 3-25, “Coprocessor 14 Clock and Power Management Summary”

2.3.4

Coprocessor 15 Register 0 – ID Register Definition

The Coprocessor 15 register may be read by software to determine the device type and revision.

The contents of this register for the PXA26x processor family is defined in the table below. This

register must read as 0x6905 2X0R where R = 0b0011 for the first stepping and then increments for

subsequent steppings, and X is the revision of the Intel® XScale™ microarchitecture present.

Please see the Intel® Developer Homepage at http://developer.intel.com for updates.

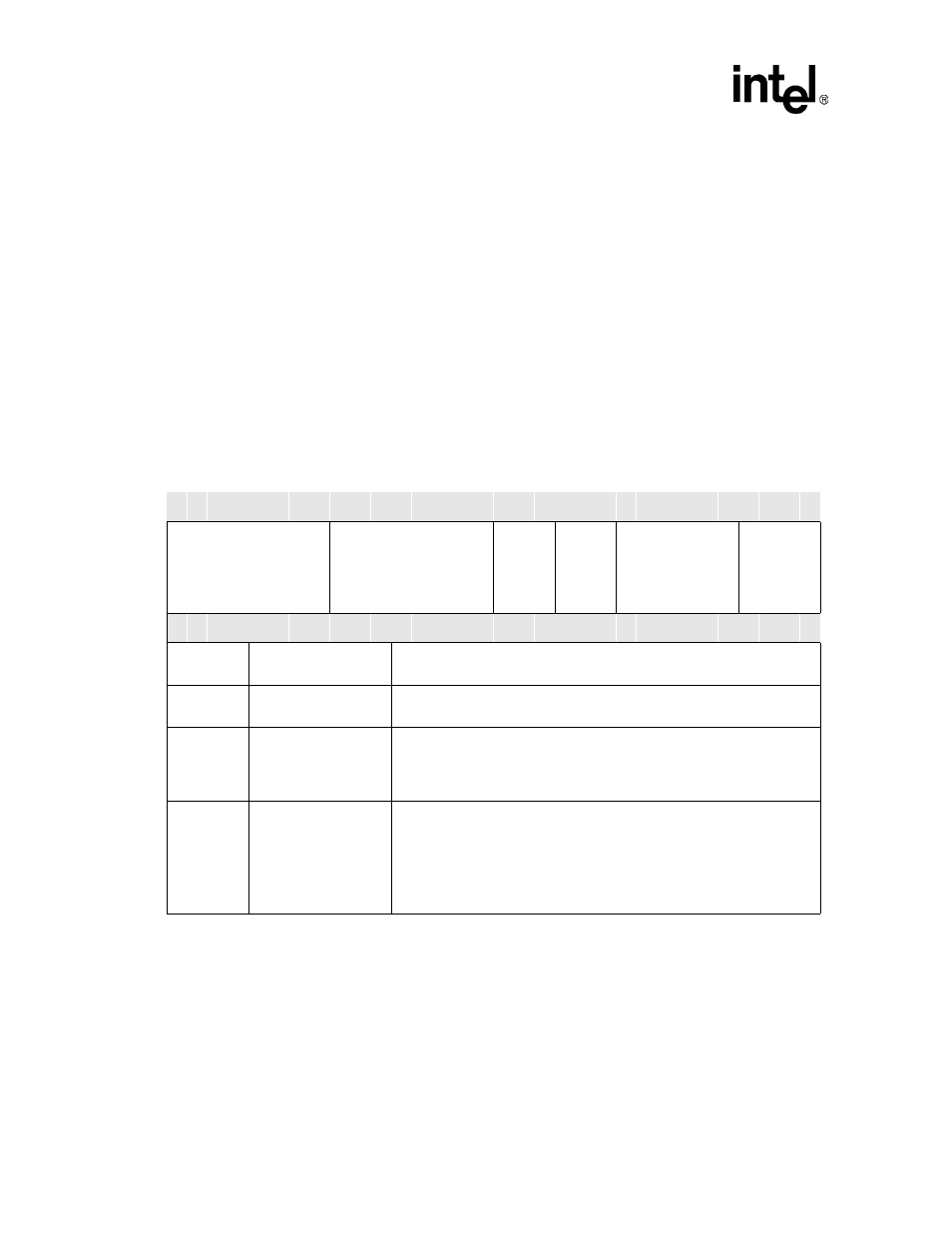

Table 2-2. ID Register Bitmap and Bit Definitions (Read-only) (Sheet 1 of 2)

CP15 Register 0

ID

CP15

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Im

ple

m

entation

T

radem

ar

k

Arc

h

it

e

c

tu

re

Ve

rs

io

n

Co

re

gen

er

ation

Co

re

Re

v

is

io

n

P

roduct

N

u

m

ber

P

roduct

Re

v

is

io

n

Reset

0

1

1

0

1

0

0

1

0

0

0

0

0

1

0

1

0

0

1

0

1

1

0

1

0

0

0

0

0

1

0

1

[31:16]

Implementation

Trademark

Implementation trademark.

0x69 – Intel® Corporation.

[23:16]

Architecture

Version

ARM* Architecture version of the core.

0x05 – ARM* architecture version 5TE

[15:13]

Core Generation

This field is updated when new sets of features are added to the core. This

allows software that is dependant on core features to target a specific core.

Core generation:

0b001 – Intel® XScale™ Core

[12:10]

Core Revision

This field is updated each time a core is revised. Differences may include

errata, software workarounds, etc.

Core revision:

0b000 – First version of the core

0b010 – Third version of the core

0b011 – Fourth version of the core