Intel PXA26X User Manual

Page 574

16-26

Intel® PXA26x Processor Family Developer’s Manual

Network/Audio Synchronous Serial Protocol Serial Ports

3

R/W

SPO

MOTOROLA SPI SSPSCLK POLARITY SETTING:

Selects the polarity of the inactive state of the SSPSCLK pin when

selecting the SPI* protocol. The SSCR1[SPO] is ignored for all data

frame formats except for the SPI* protocol (SSCR0[FRF] =0b00).

The programmed setting of the SPO alone does not determine which

SSPSCLK edge transmits or receives data; SPO in combination with

SPH does.

0 – The SSPSCLK is held low in the Inactive or Idle state when the

SSP port is not transmitting/receiving data.

1 – The SSPSCLK is held high during the Inactive or Idle state.

2

R/W

LBM

LOOP-BACK MODE (test mode bit):

Enables and disables the ability of the SSP port transmit and receive

logic to communicate.

Loop-back mode cannot be used with the Microwire* protocol since this

protocol uses half-duplex master-slave message passing.

0 – Normal SSP port operation is enabled.

1 – Output of transmit serial shifter connected to input of receive serial

shifter, internally. SSPTXD continues to function normally.

1

R/W

TIE

TRANSMIT FIFO INTERRUPT ENABLE:

Enables the transmit FIFO Service Request Interrupt.

NOTE: Clearing TIE does not affect the current state of SSSR[TFS] or

the ability of the transmit FIFO logic to set and clear

SSSR[TFS]—it blocks only the generation of the Interrupt

request. Also, the state of TIE does not effect the generation of

the transmit FIFO DMA service request, which is asserted

whenever SSSR[TFS] is set.

0 – Transmit FIFO level Interrupt is disabled. The Interrupt is masked

and the state of SSSR[TFS] is ignored.

1 – Transmit FIFO level Interrupt is enabled. Whenever SSSR[TFS] is

set, an Interrupt request is made to the Interrupt controller.

0

R/W

RIE

RECEIVE FIFO INTERRUPT ENABLE:

Enables the receive FIFO Service Request Interrupt.

NOTE: Clearing RIE does not affect the current state of SSSR[RFS] or

the ability of the receive FIFO logic to set and clear

SSSR[RFS]—it blocks only the generation of the Interrupt

request. The state of RIE does not affect the generation of the

receive FIFO DMA service request, which is asserted

whenever SSSR[RFS] is set.

0 – Receive FIFO level Interrupt is disabled. The Interrupt is masked

and SSSR[RFS] is ignored.

1 – Receive FIFO level Interrupt is enabled. Whenever SSSR[RFS] is

set, an Interrupt request is made to the Interrupt controller.

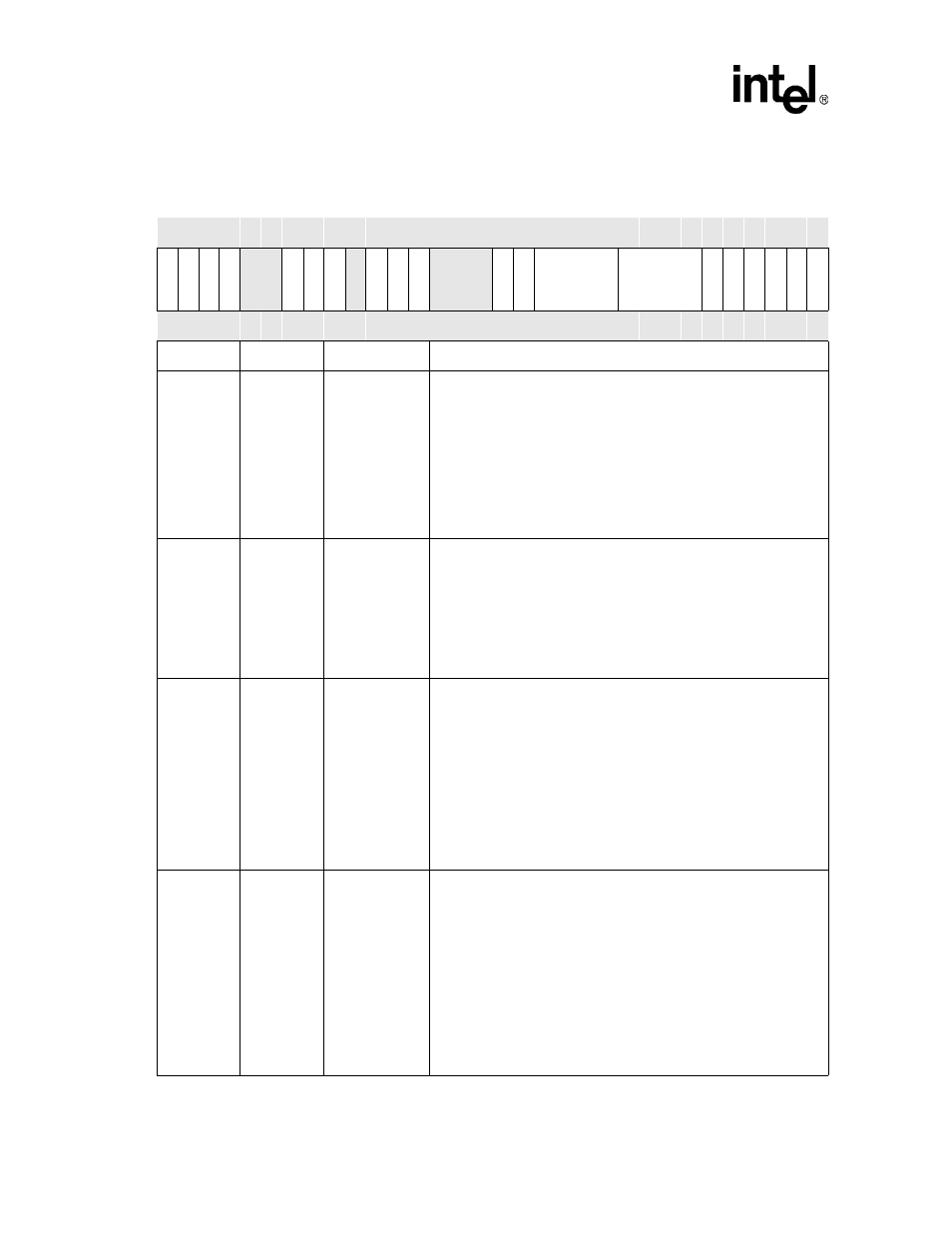

Table 16-4.

SSCR1 Bit Definitions (Sheet 6 of 6)

Physical Address

Base+0x04

SSCR1

PXA26x processor family Network/Audio

SSP Serial Ports

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

TTELP

TTE

EB

CEI

SC

F

R

Re

s

e

rv

e

d

SC

L

K

D

IR

S

F

RM

DI

R

RW

O

T

Re

s

e

rv

e

d

TS

R

E

RS

R

E

TIN

T

E

Re

s

e

rv

e

d

STRF

EFW

R

RFT

TFT

MW

D

S

SPH

SP

O

LB

M

TIE

RI

E

Reset

0

0

0

0

?

?

0

0

0

0

0

0

0

?

?

?

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Access

Name

Description