1 receive fifo service (rfs) – Intel PXA26X User Manual

Page 443

Intel® PXA26x Processor Family Developer’s Manual

12-33

Universal Serial Bus Device Controller

12.6.6

UDC Endpoint x Control/Status Register (UDCCSx), Where

x is 4, 9, or 14

The UDC endpoint(x) control/status register contains 6 bits that operate endpoint(x), an

Isochronous OUT endpoint.

12.6.6.1

Receive FIFO Service (RFS)

The receive FIFO service bit is set if the receive FIFO has one complete data packet in it and the

packet has been error checked by the UDC. A complete packet may be 256 bytes, a short packet, or

a zero packet. UDCCSx[RFS] is not cleared until all data is read from both buffers.

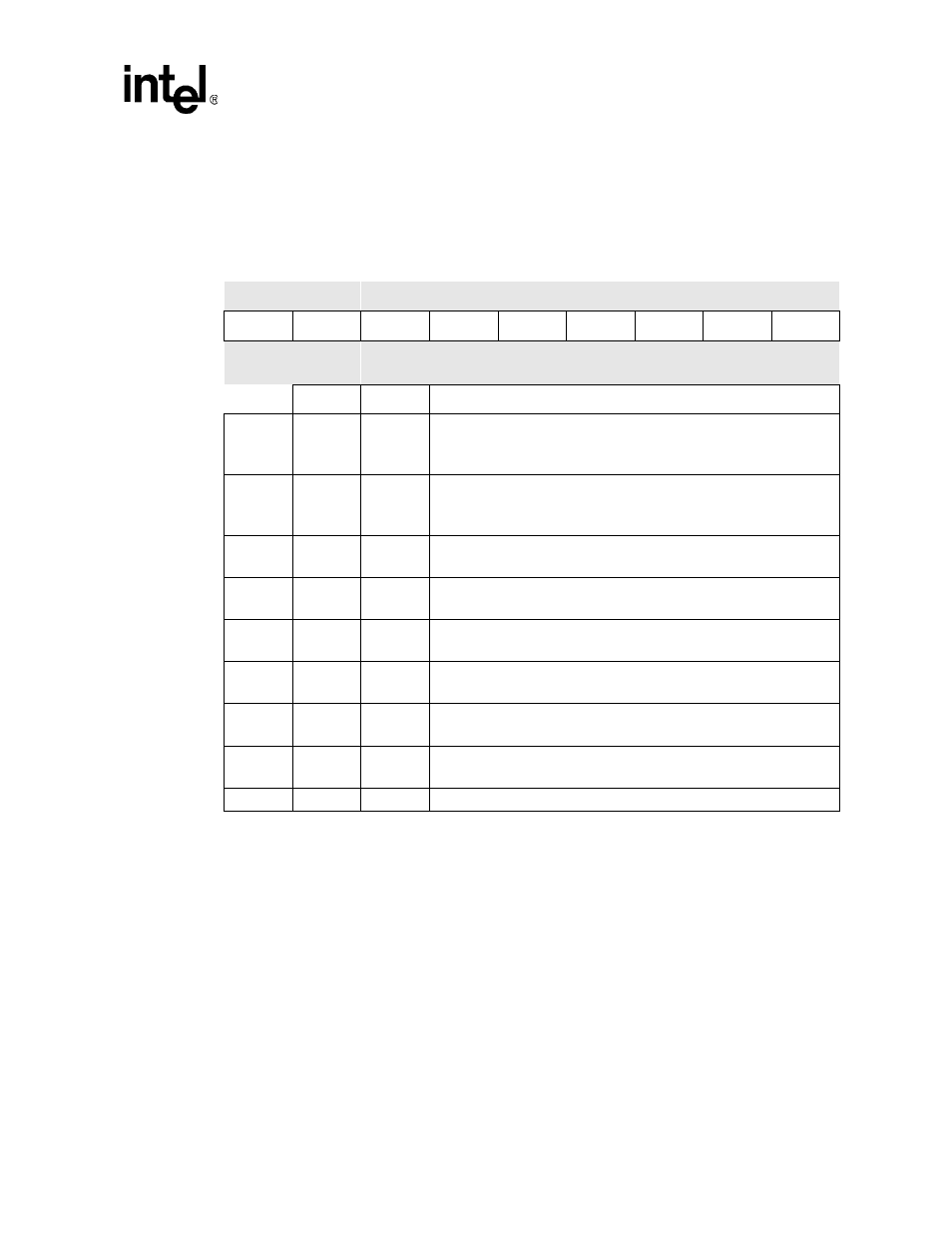

Table 12-16. UDC Endpoint x Control Status Register, Where x is 3, 8, or 13

0h 4060 001C

UDCCS3

Read/Write

0h 4060 0030

UDCCS8

Read/Write

0h 4060 0044

UDCCS13

Read/Write

Bit

31:8

7

6

5

4

3

2

1

0

Reserved

TSP

Reserved

Reserved

Reserved

TUR

FTF

TPC

TFS

Rese

t

X

0

0

0

0

0

0

0

1

Bits

Name

Description

0

TFS

TRANSMIT FIFO SERVICE (read-only):

0 – Transmit FIFO has no room for new data

1 – Transmit FIFO has room for at least 1 complete data packet

1

TPC

TRANSMIT PACKET COMPLETE (read/write 1 to clear):

0 – Error/status bits invalid.

1 – Transmit packet has been sent and error/status bits are valid.

2

FTF

FLUSH Tx FIFO (always read 0/ write a 1 to set):

1 – Flush Contents of TX FIFO

3

TUR

TRANSMIT FIFO UNDERRUN (read/write 1 to clear):

1 – Transmit FIFO experienced an underrun.

4

—

Reserved

Always reads 0

5

—

Reserved

Always reads 0.

6

—

Reserved

Always reads 0

7

TSP

TRANSMIT SHORT PACKET (read/write 1 to set):

1 – Short packet ready for transmission.

31:8

—

Reserved for future use