Figure 42. reti instruction sequence, Return from subroutine (reti) instruction sequence, When the – Zilog Z80180 User Manual

Page 99

Z8018x

Family MPU User Manual

84

UM005003-0703

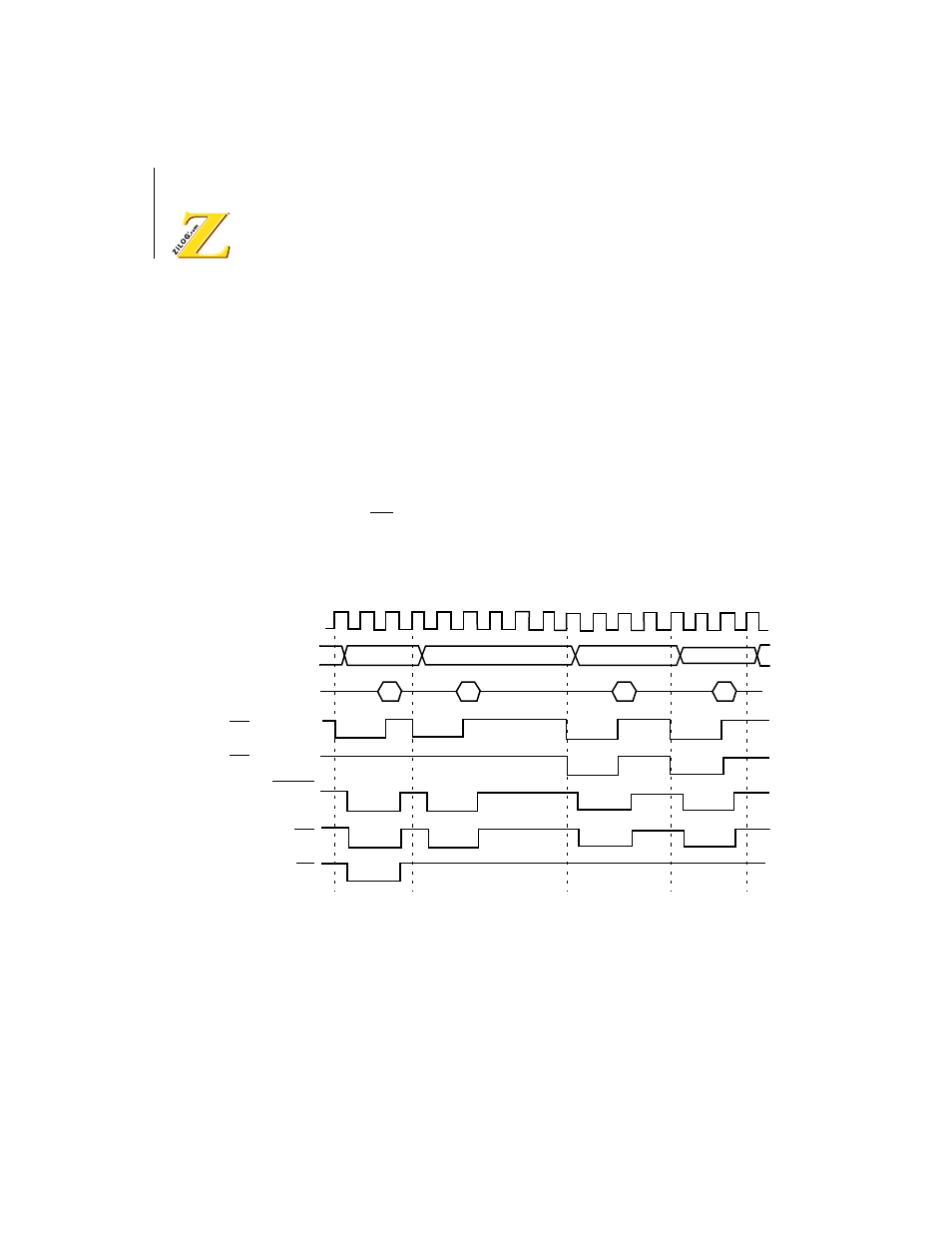

Return from Subroutine (RETI) Instruction Sequence

When the

EDH

/

4DH

sequence is fetched by the Z8X180, it is recognized as

the RETI instruction sequence. The Z8X180 then refetches the RETI

instruction with four T-states in the

EDH

cycle allowing the Z80

peripherals time to decode that cycle (See Figure 42). This procedure

allows the internal interrupt structure of the peripheral to properly decode

the instruction and behave accordingly.

The M1E bit of the Operation Mode Control Register (OMCR) must be

set to

0

so that M1 signal is active only during the refetch of the RETI

instruction sequence. This condition is the desired operation when Z80

peripherals are connected to the Z8018X.

Figure 42. RETI Instruction Sequence

The RETI instruction takes 22 T-states and 10 machine cycles. Table 10

lists the conditions of all the control signals during this sequence for the

RD

MREQ

D0

–

D7

T1

ST

Phi

T3

Ti

Ti

Ti

T1

T2

T3

Ti

T1

T2

T3

T1

T3 T1

T2

T2

PC

PC + 1

PC

PC + 1

4DH

4DH

EDH

EDH

M1 (M1E = 0)

M1 (M1E = 1)

A0

–

A18 (A19)

Note: RETI machine cycles 9 and 10 not shown.