Figure 69. e clock timing in sleep mode and, System stop mode, On-chip clock generator – Zilog Z80180 User Manual

Page 183

Z8018x

Family MPU User Manual

168

UM005003-0703

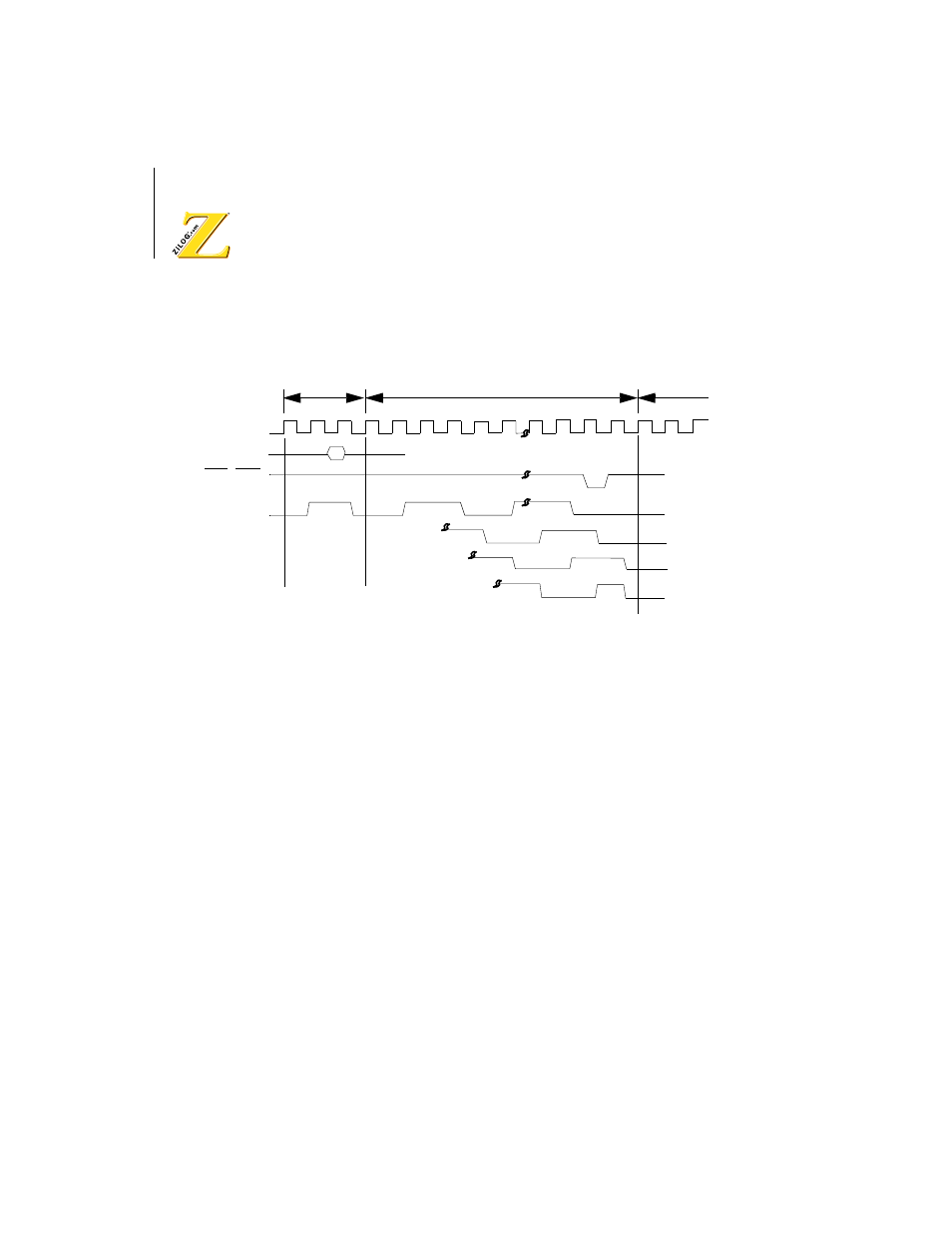

Figure 69. E Clock Timing in SLEEP Mode and SYSTEM STOP Mode

On-Chip Clock Generator

The Z8X180 contains a crystal oscillator and system clock generator. A

crystal can be directly connected or an external clock input can be

provided. In either case, the system clock is equal to one-half the input

clock. For example, a crystal or external clock input of 8 MHz

corresponds with a system clock rate of 4 MHz.

Z8S180 and Z8L180-class processors also have the ability to run at X1

and X2 input clock.

Table 25 describes the AT cut crystal characteristics (Co, Rs) and the load

capacitance (CL1, CL2) required for various frequencies of Z8X180

operation.

E

E

E

T1

T2

T3

Ts

T1

T1

T2

T2

Ts

Ts

Ts

76H

SLP

Instruction

2nd Op Code

Fetch Cycle

SLEEP mode or SYSTEM STOP mode

Op Code

Fetch Cycle

E

Phi

D0

–

D7

INT, NMI