Zilog Z80180 User Manual

Page 138

Z8018x

Family MPU User Manual

UM005003-0703

123

ASCI Control Register A0, 1 (CNTLA0, 1)

Each ASCI channel Control Register A configures the major operating modes

such as receiver/transmitter enable and disable, data format, and multiprocessor

communication mode.

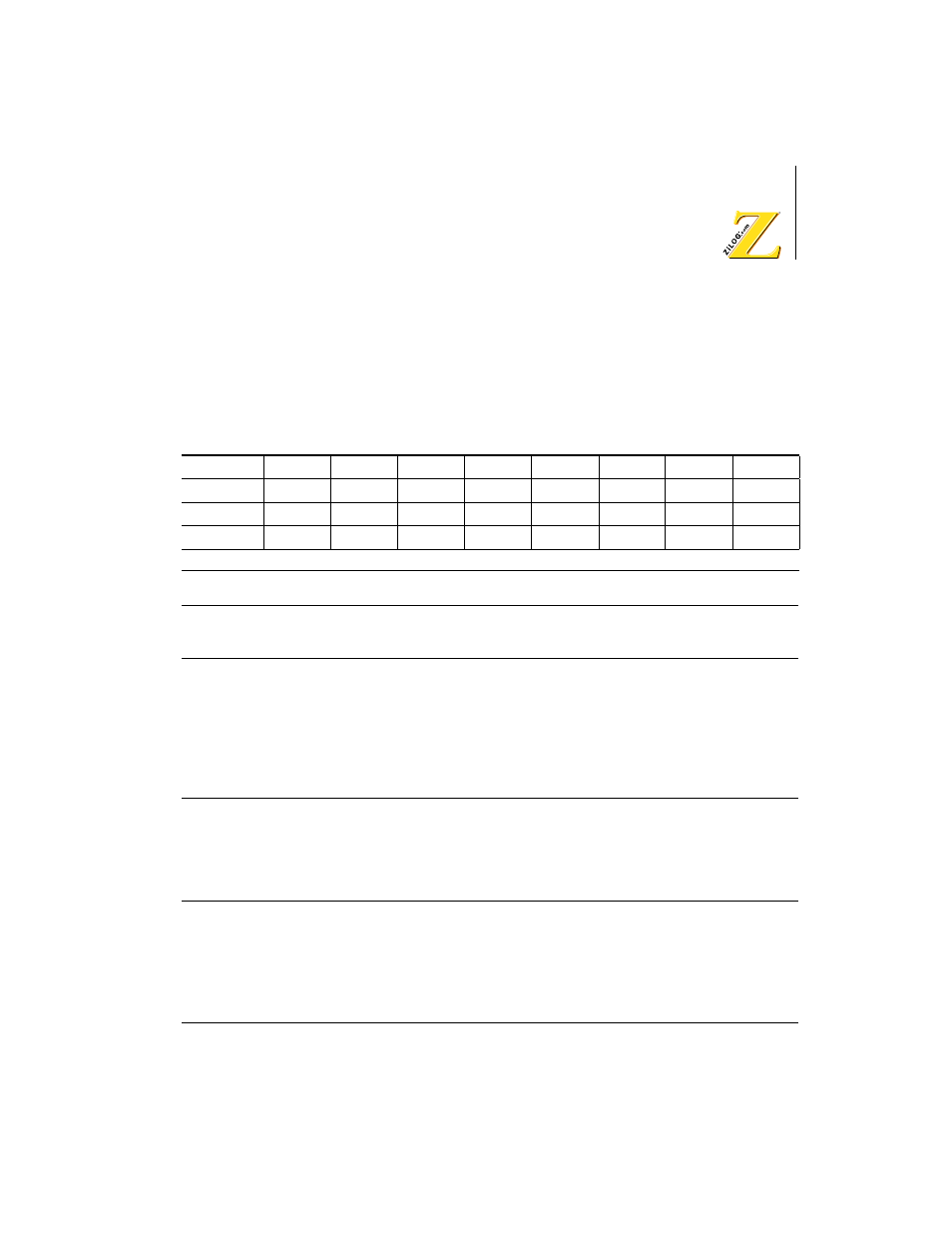

ASCI Status Register 1 (STAT1: 05H)

Bit

7

6

5

4

3

2

1

0

Bit/Field

RDRF

OVRN

PE

FE

RIE

CTS1E

TDRE

TIE

R/W

R

R

R

R

R/W

R/W

R

R/W

Reset

0

0

0

0

0

0

0

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

Bit

Position Bit/Field R/W

Value

Description

7

RDRF

R

Receive Data Register Full — RDRF is set to 1 when an

incoming data byte is loaded into RDR. Note that if a

framing or parity error occurs, RDRF is still set and the

receive data (which generated the error) is still loaded

into RDR. RDRF is cleared to 0 by reading RDR, when

the DCD0 input is High, in IOSTOP mode, and during

RESET.

6

OVRN

R

Overrun Error — OVRN is set to 1 when RDR is full

and RSR becomes full. OVRN is cleared to 0 when the

EFR bit (Error Flag Reset) of CNTLA is written to 0,

when DCD0 is High, in IOSTOP mode, and during

RESET.

5

PE

R

Parity Error — PE is set to 1 when a parity error is

detected on an incoming data byte and ASCI parity

detection is enabled (the MOD1 bit of CNTLA is set to

1). PE is cleared to 0 when the EFR bit (Error Flag Reset)

of CNTLA is written to 0, when DCD0 is High, in

IOSTOP mode, and during RESET.