Zilog Z80180 User Manual

Page 103

Z8018x

Family MPU User Manual

88

UM005003-0703

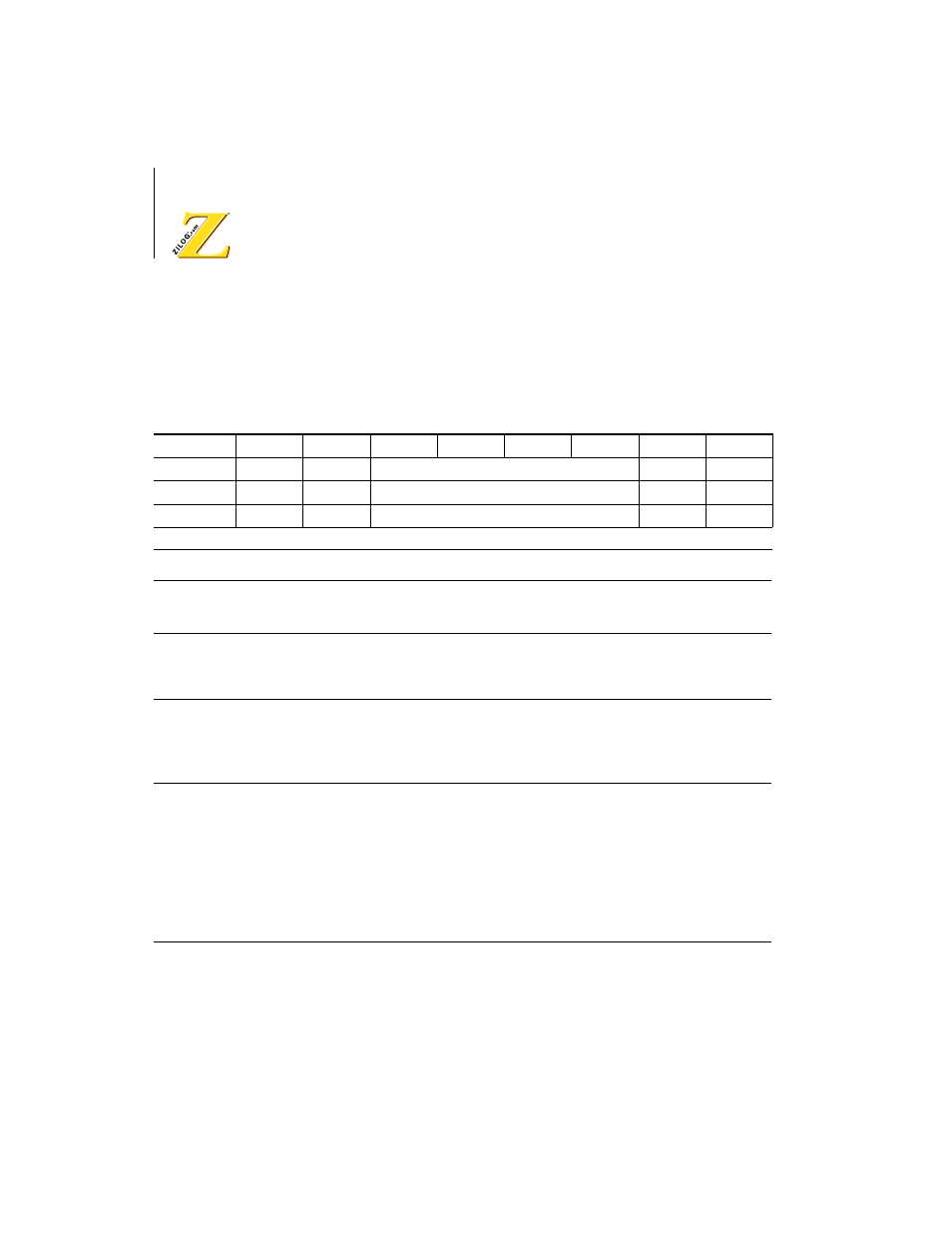

Refresh Control Register (RCR)

The RCR specifies the interval and length of refresh cycles, while

enabling or disabling the refresh function.

Refresh Control Register (RCR: 36H)

Bit

7

6

5

4

3

2

1

0

Bit/Field

REFE

REFW

?

CYC1

CYC0

R/W

R/W

R/W

?

R/W

R/W

Reset

1

1

?

0

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

Bit

Position Bit/Field R/W

Value

Description

7

REFE

R/W

0

1

REFE: Refresh Enable

Disables the refresh controller

Enables refresh cycle insertion.

6

REFW

R/W

0

1

Refresh Wait (bit 6)

Causes the refresh cycle to be two clocks in duration.

Causes the refresh cycle to be three clocks in duration by

adding a refresh wait cycle (TRW).

1

–

0

CYC1

–

0 R/W

Cycle Interval — CYC1 and CYC0 specify the interval

(in clock cycles) between refresh cycles. In the case of

dynamic RAMs requiring 128 refresh cycles every 2 ms

(or 256 cycles in every 4 ms), the required refresh interval

is less than or equal to 15.625

ms. Thus, the underlined

values indicate the best refresh interval depending on

CPU clock frequency. CYC0 and CYC1 are cleared to 0

during RESET. Refer to Table 11.