Bus control signal conditions, Table 51 – Zilog Z80180 User Manual

Page 267

Z8018x

Family MPU User Manual

251

UM005003-0703

Bus Control Signal Conditions

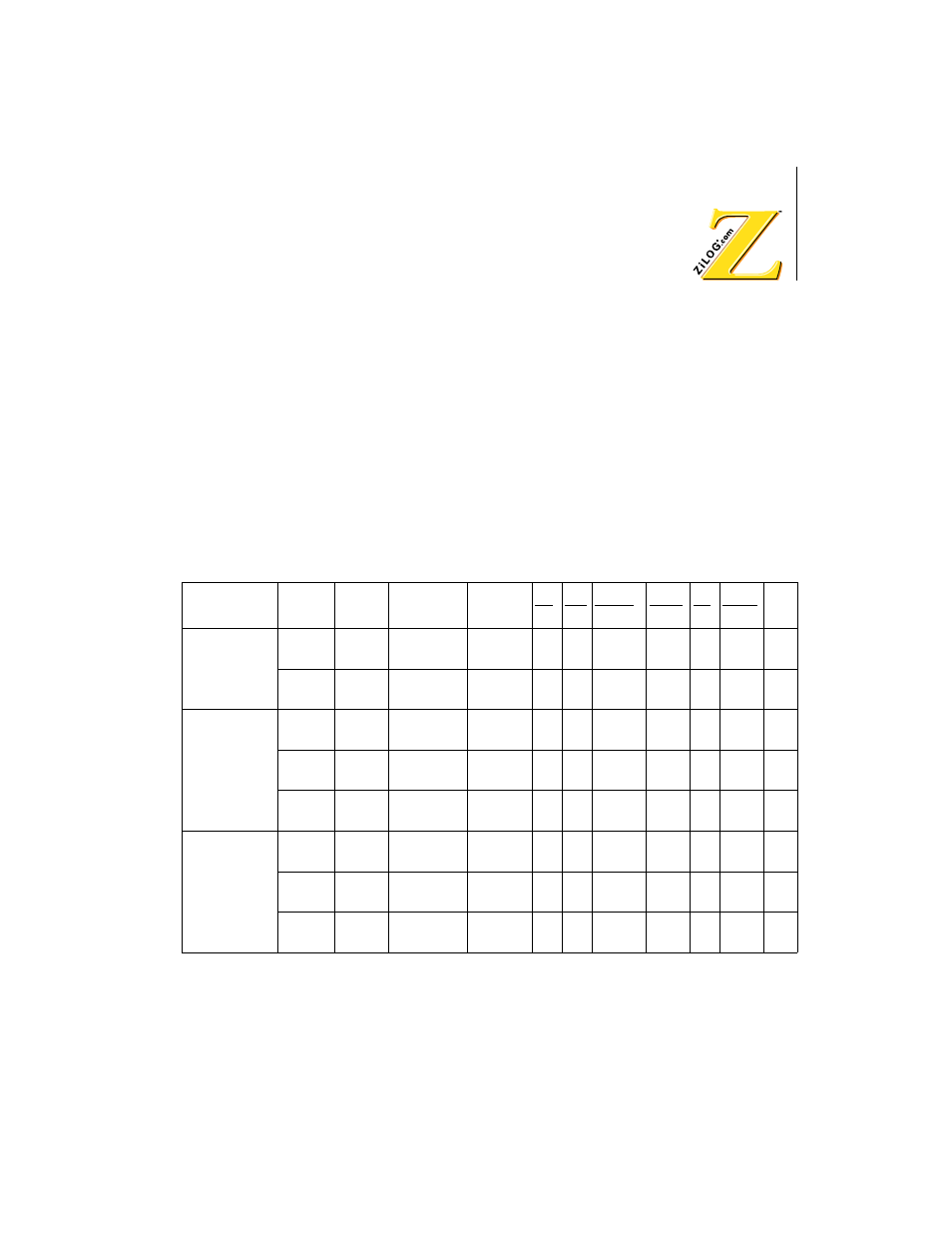

BUS AND CONTROL SIGNAL CONDITION IN EACH MACHINE

CYCLE

* (ADDRESS) invalid

Z (DATA) high impedance.

** added new instructions to Z80

Table 51. Bus and Control Signal Condition in Each Machine Cycle

Instruction

Machine

Cycle

States

Address

Data

RD WR MREQ

IORQ M1 HALT ST

ADD HL,ww

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

~MC5

TiTiTiTi *

Z

1

1

1

1

1

1

1

ADD IX,xx

ADD IY,yy

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

T1T2T3 2nd Op Code

Address

2nd Op

Code

0

1

0

1

0

1

1

MC3

~MC6

TiTiTiTi *

Z

1

1

1

1

1

1

1

ADC HL,ww

SBC HL,ww

MC1

T1T2T3 1st Op Code

Address

1st Op

Code

0

1

0

1

0

1

0

MC2

T1T2T3 2nd Op Code

Address

2nd Op

Code

0

1

0

1

0

1

1

MC3

~MC6

TiTiTiTi *

Z

1

1

1

1

1

1

1