Table 8, State of ief1 and ief2 – Zilog Z80180 User Manual

Page 84

Z8018x

Family MPU User Manual

UM005003-0703

69

If IEF1 is

0

, all maskable interrupts are disabled. IEF1 can be reset to

0

by

the DI (Disable Interrupts) instruction and set to

1

by the El (Enable

Interrupts) instruction.

The purpose of IEF2 is to correctly manage the occurrence of NMI.

During NMI, the prior interrupt reception state is saved and all maskable

interrupts are automatically disabled (IEF1 copied to IEF2 and then IEF1

cleared to

0

). At the end of the NMI interrupt service routine, execution of

the RETN (Return from Non-maskable Interrupt) automatically restores

the interrupt receiving state (by copying IEF2 to IEF1) prior to the

occurrence of NMI.

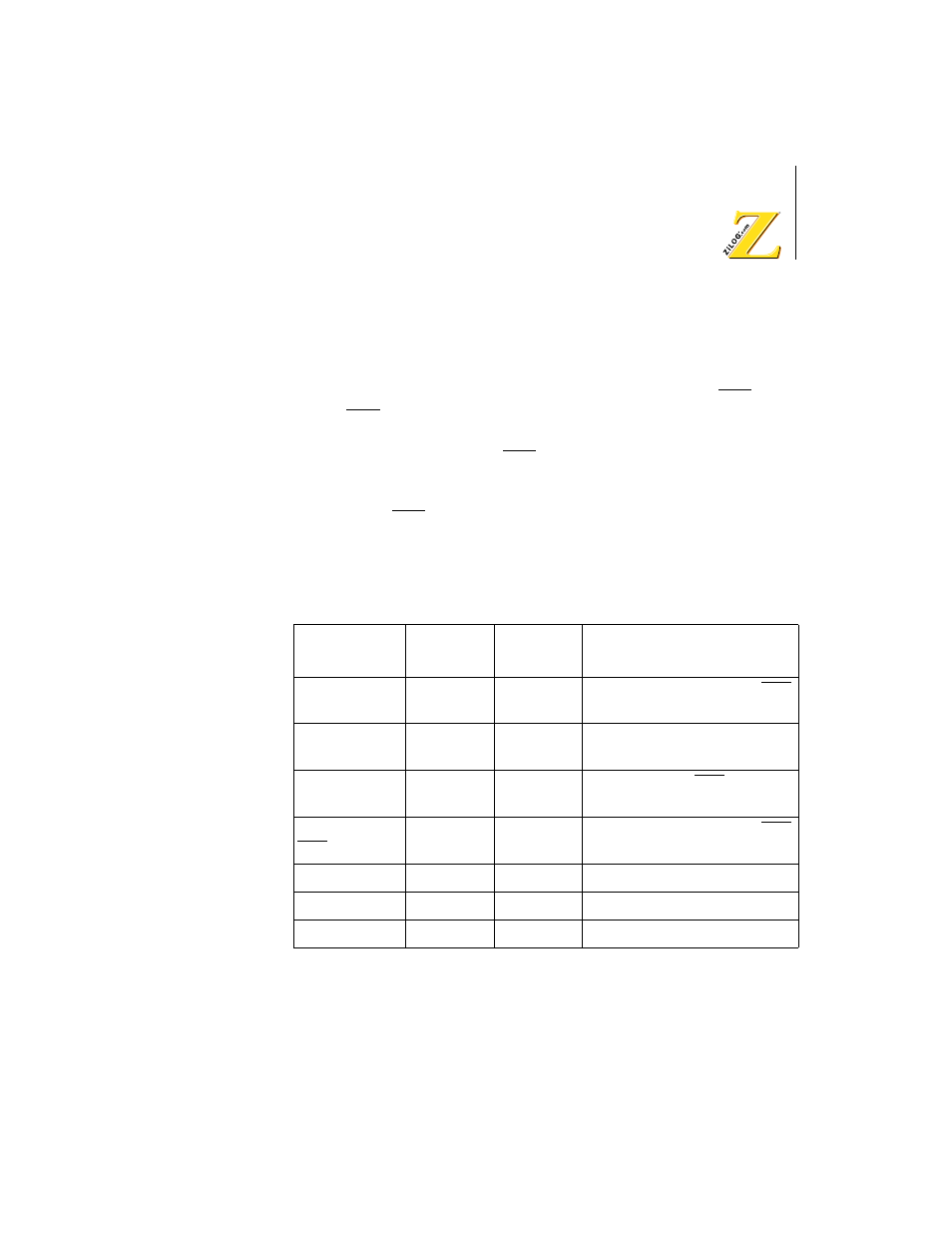

Table 8 describes how the IEF2 state can be reflected in the P/V bit of the

CPU Status Register by executing LD A, I or LD A, R instructions.

Table 8.

State of IEF1 and IEF2

CPU

Operation

IEF1

IEF2

REMARKS

RESET

0

0

Inhibits the interrupt except NMI

and TRAP.

NMI

0

IEF1

Copies the contents of IEF1 to

IEF2

RETN

IEF2

not affected Returns from the NMI service

routine.

Interrupt except

NMI end TRAP

0

0

Inhibits the interrupt except NMI

end TRAP

RETI

not affected not affected

TRAP

not affected not affected

EI

1

1