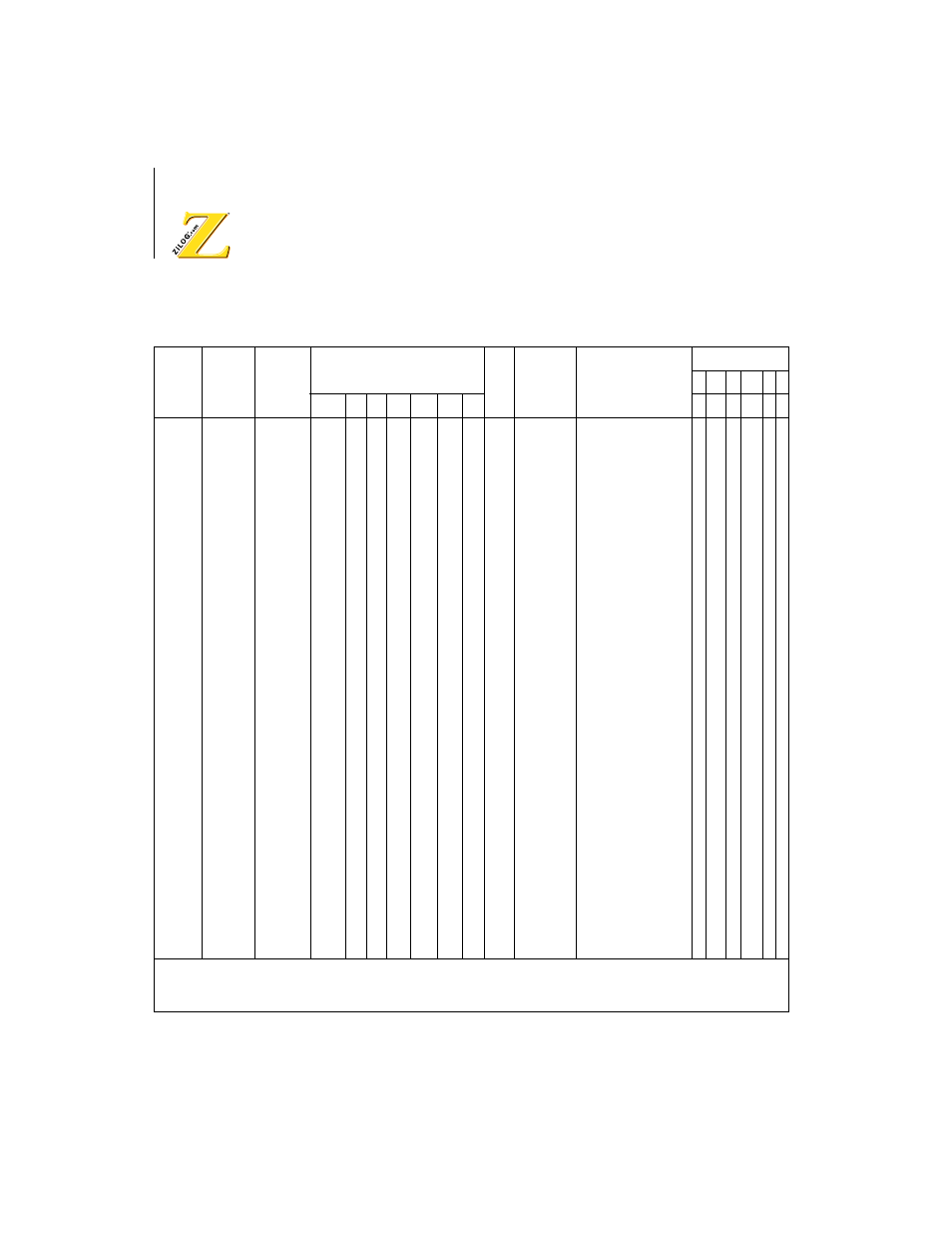

Table 43. block transfer (continued) – Zilog Z80180 User Manual

Page 242

Z8018x

Family MPU User Manual

226

UM005003-0703

CPI

11101101

S

S

2

12

Ar-(HL)

M

S

·

10100001

BC

R

-1

®BC

R

HL

R

+ 1

®HL

R

(3)

(2)

CPIR

11101101

S

S

2

14

BC

R

¹ 0 Ar*(HL)

M

S

·

10110001

12

BC

R

= 0 or Ar = (HL)

M

Ar-(HL)

M

Q

BC

R

-1

®BC

R

HL

R

+ 1

®HL

R

Repeat Q until

Ar = (HL)

M

or BC

R

= 0

(2)

LDD

11 101 101

S/D

2

12

(HL)

M

® (DE)

M

· ·

R

R

·

10 101 000

BC

R

-1

®BC

R

DE

R

-1

®DE

R

HL

R

-1

®HL

R

LDDR

11 101 101

S/D

2

14(BC

R

¹ 0)

(HL)

M

® (DE)

M

BC

R

-1

® BC

R

Q

DE

R

-1

® DE

R

HL

R

-1

® HL

R

· ·

R R

R

·

10 111 000

12(BC

R

= 0)

Repeat Q until

BC

R

= 0

(2)

LDI

11 101 101

S/D

2

12

(HL)

M

®DE)

R

· ·

R

R

·

10 100 000

BC

R

-1

®BC

R

DE

R

+ 1

®DE

R

HL

R

+ 1

®HL

R

LDIR

11 101 101

S/D

2

14(BC

R

¹0)

(HL)

M

®(DE)

M

Q

BC

R

-1

®BC

R

DE

R

+ 1

®DE

R

HL

R

+ 1

®HL

R

· ·

R R

R

·

10 110 000

12(BC

R

= 0)

Repeat Q until

BC

R

= 0

(2) P/V = 0: BC

R

-1 = 0

P/V = 1: BC

R

-1

¹ 0

(3) Z = 1: Ar = (HL)

M

Z = 0 :Ar

¹ (HL)

M

Table 43. Block Transfer (Continued)

Operation

Name

Mnemonics Op Code

Addressing

Bytes States

Operation

Flags

7 6

4 2

1 0

Immed Ext Ind Reg RegI Imp Rel

S Z

H P/V N C