Zilog Z80180 User Manual

Page 62

Z8018x

Family MPU User Manual

UM005003-0703

47

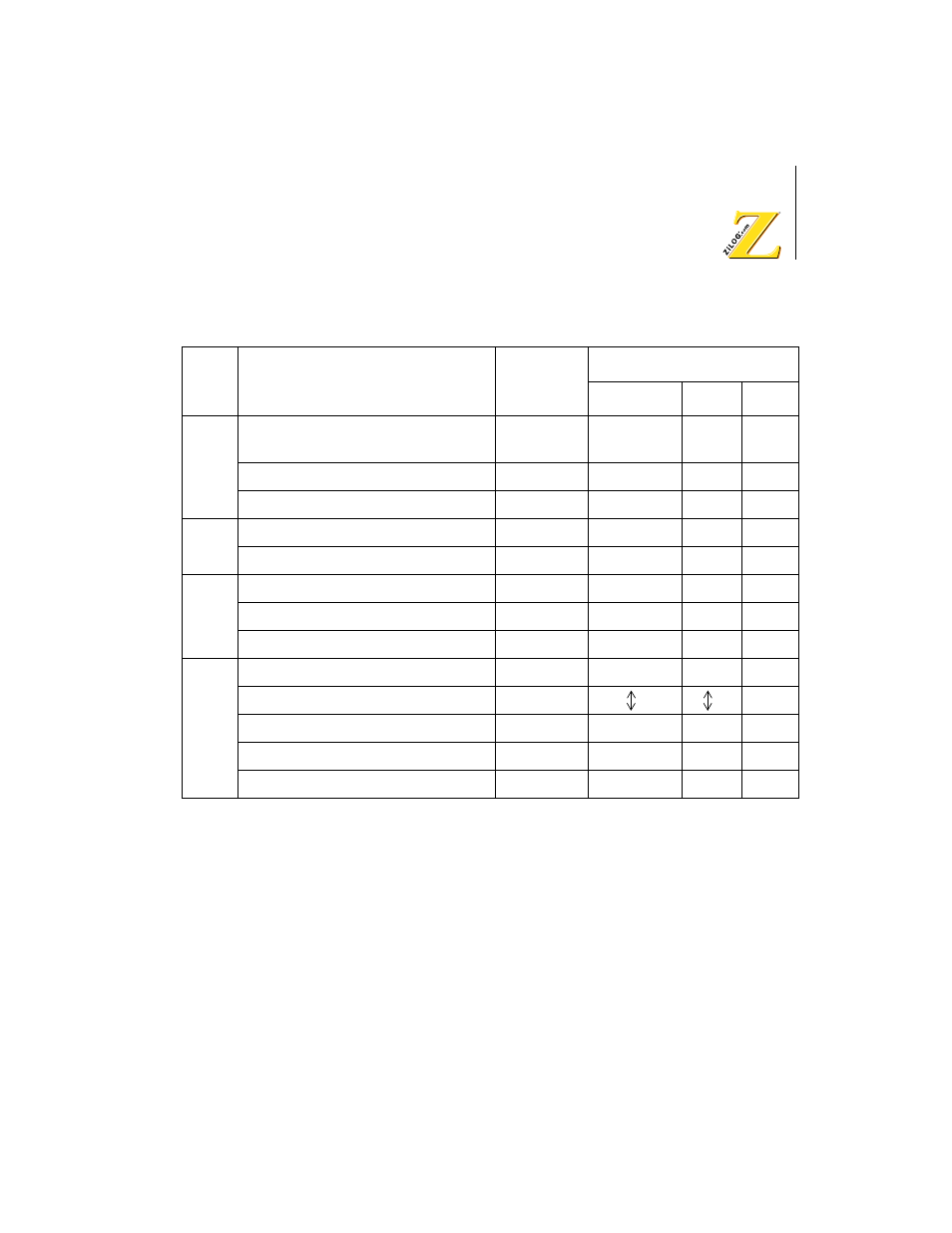

INT

IL Register (Interrupt Vector Low

Register)

IL

XX110011

33H

INT/TRAP Control Register

ITC

XX110100

34H

Reserved

XX110101

35H

Refresh Refresh Control Register

RCR

XX110110

36H

Reserved

XX110111

37H

MMU MMU Common Base Register

CBR

XX111000

38H

MMU Bank Base Register

BBR

XX111001

39H

MMU Common/Bank Area Register

CBAR

XX111010

3AH

I/O

Reserved

XX111011

3BH

XX111101

3DH

Operation Mode Control Register

OMCR

XX111110

3EH

I/O Control Register

ICR

XX111111

3FH

Table 6.

I/O Address Map for Z80180-Class Processors Only (Continued)

Register

Mnemonic

Address

Binary

Hex

Page