Figure 46. dma timing diagram-cycle steal mode, With dwe0 – Zilog Z80180 User Manual

Page 121

Z8018x

Family MPU User Manual

106

UM005003-0703

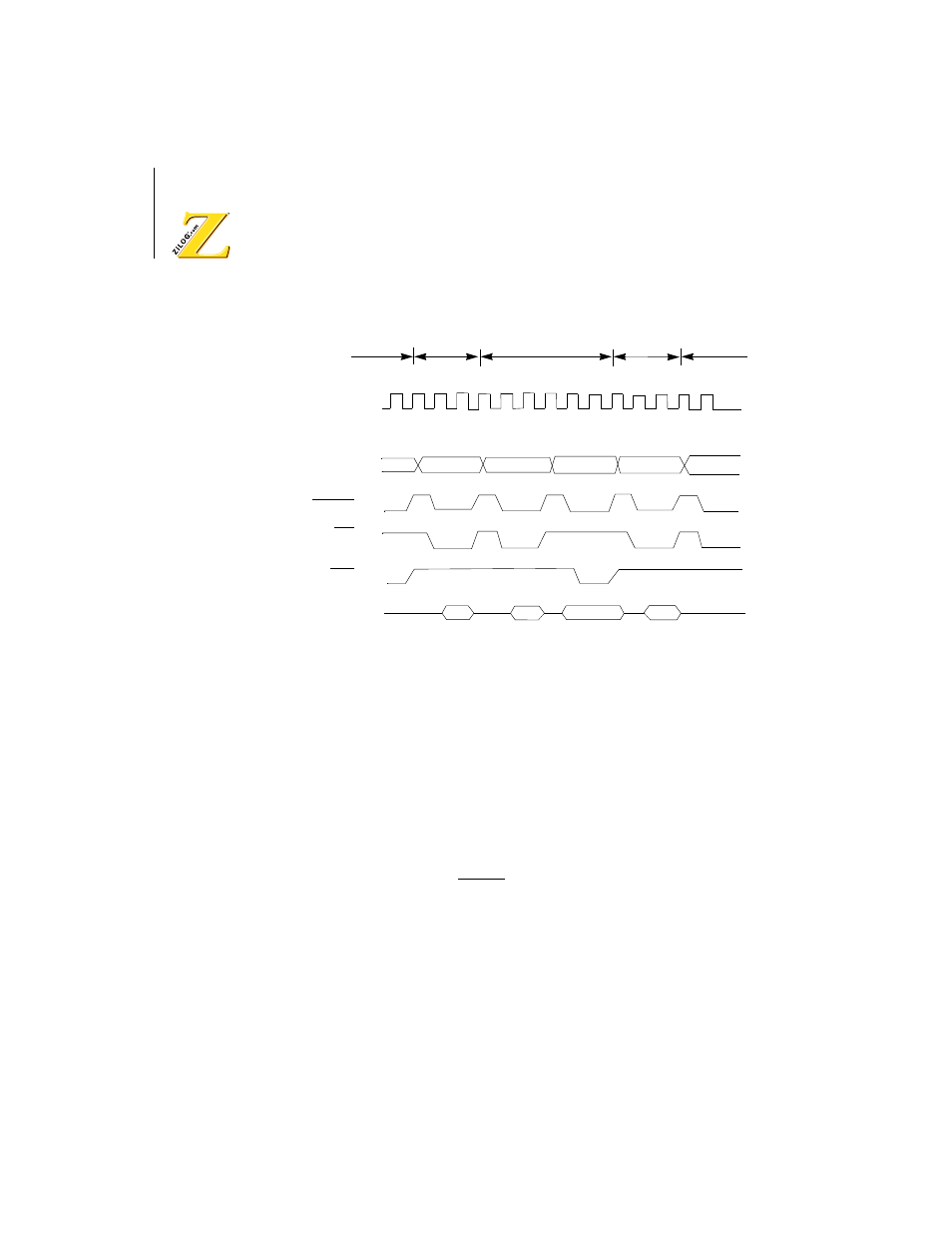

Figure 46. DMA Timing Diagram-CYCLE STEAL Mode

To initiate memory to/from memory DMA transfer for channel 0, perform

the following operations.

1. Load the memory source and destination address into SAR0 and DAR0

2. Specify memory to/from memory mode and address increment/

decrement in the SM0 SM1, DM0 and DM1 bits of DMODE.

3. Load the number of bytes to transfer in BCR0.

4. Specify burst or cycle steal mode in the MMOD bit of DCNTL.

5. Program DE0 =

1

(with DWE0 =

0

in the same access) in DSTAT and

the DMA operation starts one machine cycle later. If interrupt occurs

at the same time, the DIE0 bit must be set to

1

.

T1 T2

T1 T2

T1 T2

T1

T3

T3

T3

T2

T3

T1 T2

DMA cycle

CPU cycle

DMA cycle (transfer 1 byte)

CPU cycle

DMA cycle

LD g,m

Op Code

Source

memory

Destination

memory

LD g,m

operand

WR

MREQ

Address

Data

RD

m

Read data

Phi

Write data,

m

address

address

address

address