Table 10, Reti control signal states – Zilog Z80180 User Manual

Page 100

Z8018x

Family MPU User Manual

UM005003-0703

85

Z8X180. Figure 43 illustrates the INT1, INT2 and internal interrupts

timing.

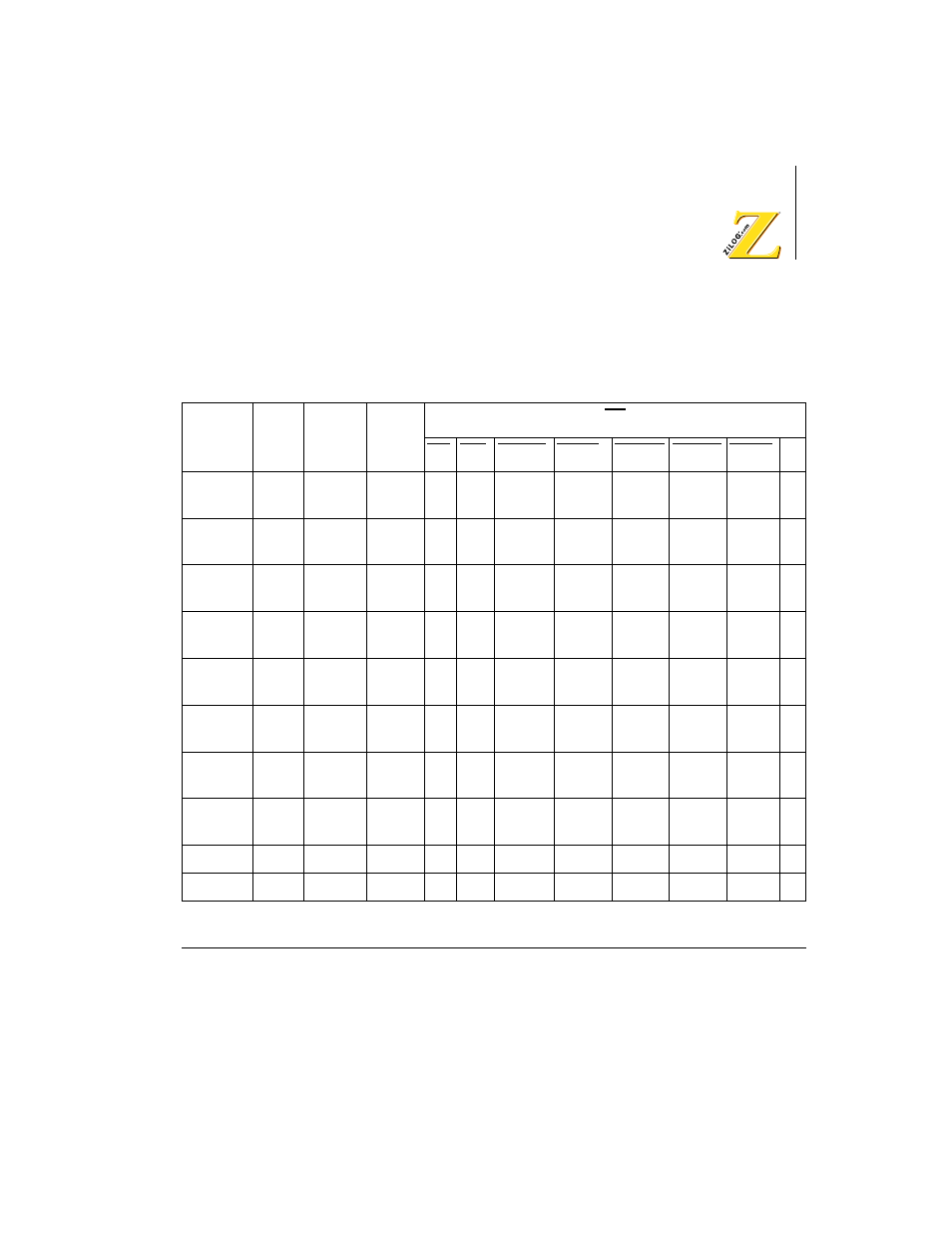

Table 10. RETI Control Signal States

Machine

Cycle

States Address Data

MI

RD WR MREQ IORQ M1E=1 M1E=0 HALT ST

1

T1-T3 1st

Op Code

EDH

0

1

0

1

0

1

1

0

2

TI-T3 2nd

Op Code

4DH

0

1

0

1

0

1

1

1

3

T1

Don't

Care

3-state

1

1

1

1

1

1

1

1

4

T1

Don't

Care

3-state

1

1

1

1

1

1

1

1

5

T1

Don't

Care

3-state

1

1

1

1

1

1

1

1

6

T1-T3 1st

Op Code

EDH

0

1

0

1

0

0

1

1

7

T1

Don't

Care

3-state

1

1

1

1

1

1

1

1

8

T1-T3 2nd

Op Code

4DH

0

1

0

1

0

1

1

1

9

T1-T3 SP

data

0

1

0

1

1

1

1

1

10

T1-T3 SP+1

data

0

1

0

1

1

1

1

1

IOC affects the IORQ/RD signals. M1E affects the assertion of M1. One state also reflects a 1 while

the other reflects a 0