Table 12, Channel 0 destination – Zilog Z80180 User Manual

Page 113

Z8018x

Family MPU User Manual

98

UM005003-0703

3

–

2

SM1:0

W

Source Mode Channel — Specifies whether the source

for channel 0 transfers is memory, I/O, or memory

mapped I/O and the corresponding address modifier.

Reference Table 13.

1

MMOD

R/W

DMA Memory Mode Channel 0 — When channel 0 is

configured for memory to/from memory transfers, the

external

DREQ

0 input is not used to control the transfer

timing. Instead, two automatic transfer timing modes are

selectable - BURST (MMOD is 1) and CYCLE STEAL

(MMOD is 0). For BURST memory to/from memory

transfers, the DMAC takes control of the bus

continuously until the DMA transfer completes (as shown

by the byte count register is 0). In CYCLE STEAL mode,

the CPU is given a cycle for each DMA byte transfer

cycle until the transfer is completed.

For channel 0 DMA with I/O source or destination, the

DREQ

0 input times the transfer and thus MMOD is

ignored.

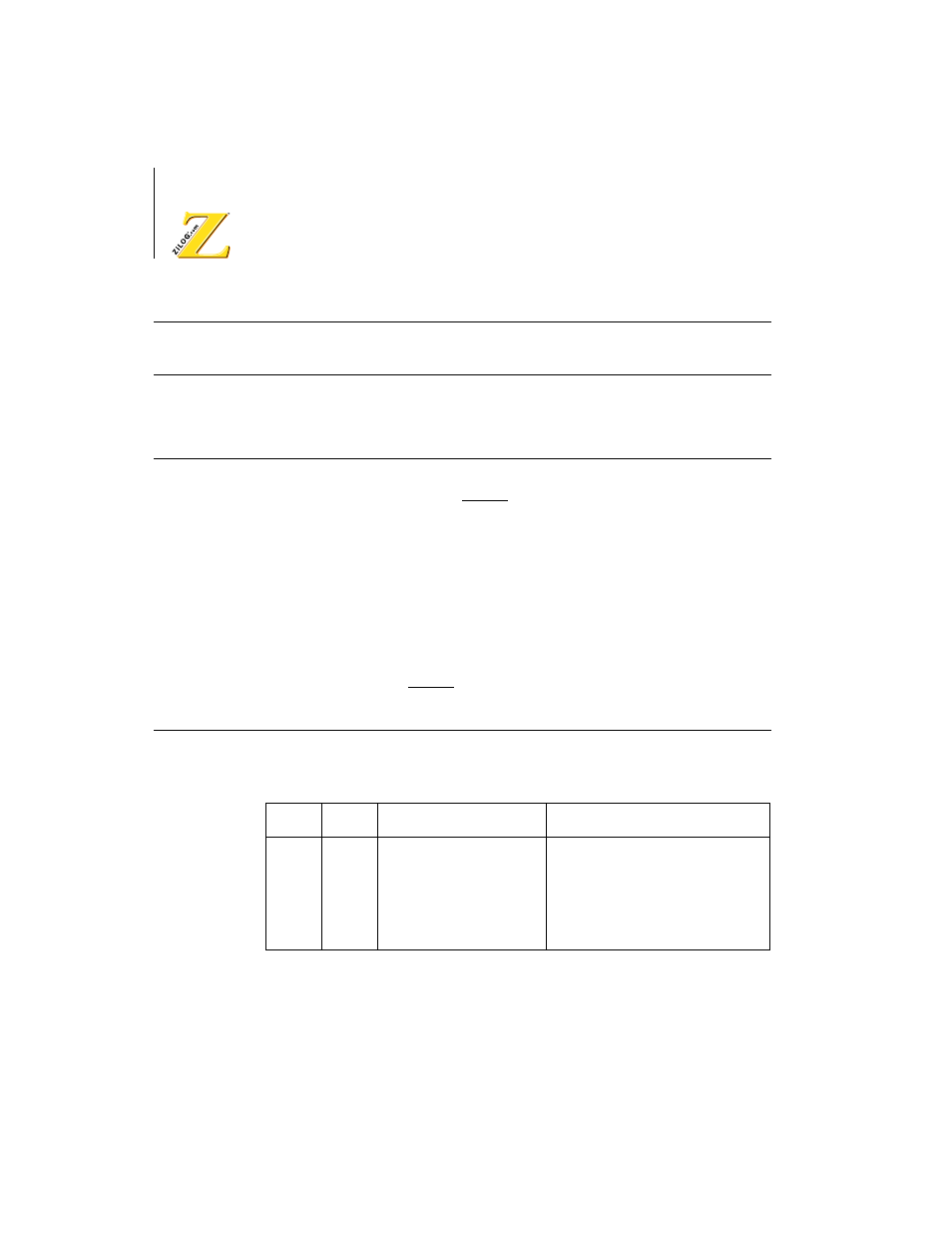

Table 12. Channel 0 Destination

DM1

DM0

Memory/I/O

Address Increment/Decrement

0

0

Memory

+

1

0

1

Memory

-1

1

0

Memory fixed

1

1

I/O

fixed

Bit

Position Bit/Field R/W

Value

Description