Table 24, E clock timing in each condition – Zilog Z80180 User Manual

Page 181

Z8018x

Family MPU User Manual

166

UM005003-0703

These devices require connection with the Z8X180 synchronous E clock

output. The speed (access time) required for the peripheral devices are

determined by the Z8X180 clock rate. Table 24, and Figure 67 through

Figure 70 define E clock output timing.

Wait States are inserted in Op Code fetch, memory read/write, and I/O

read/write cycles which extend the duration of E clock output High.

During I/O read/write cycles with no Wait States (only occurs during on-

chip I/O register accesses), E does not go High.

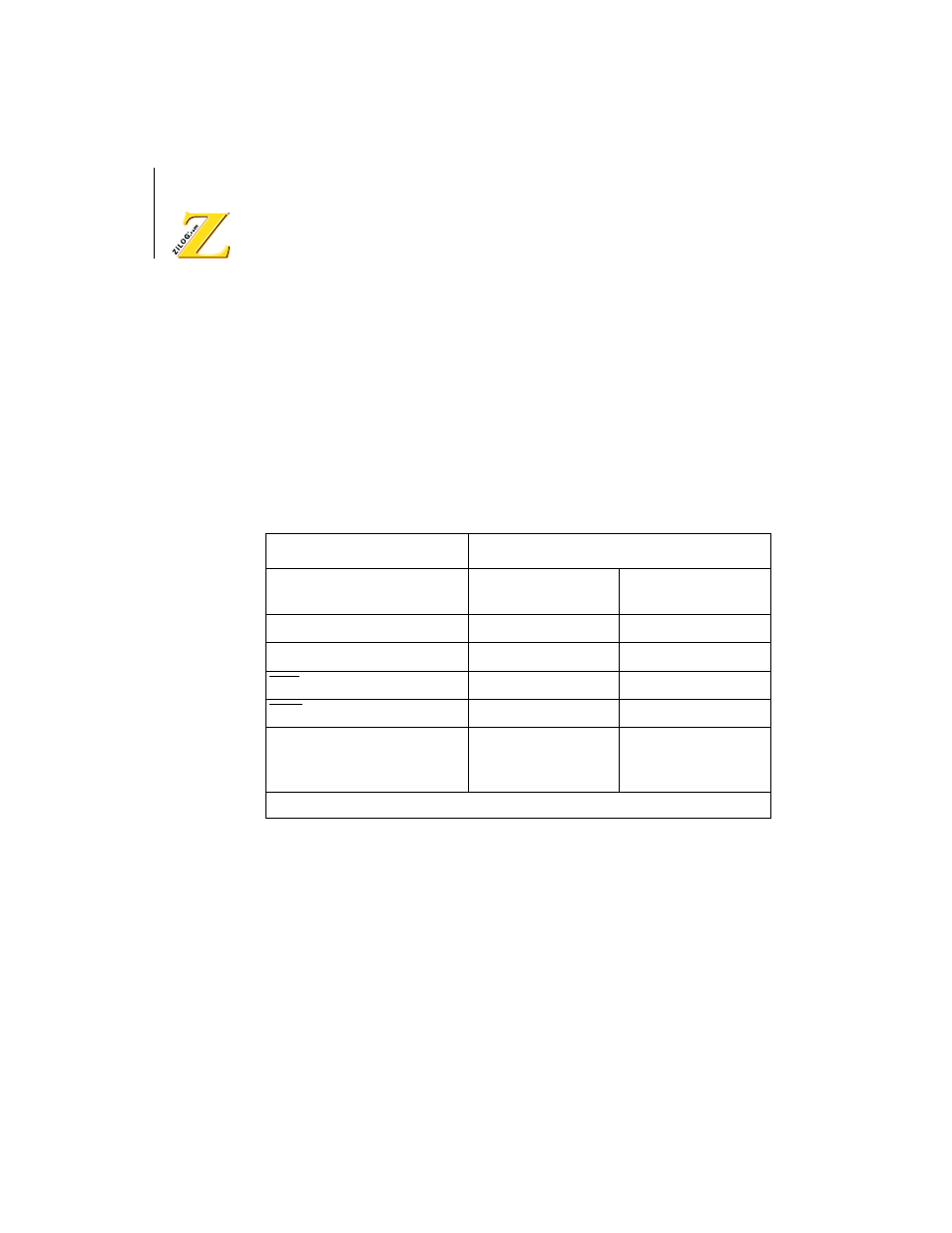

Table 24. E Clock Timing in Each Condition

Condition

Duration of E Clock Output High

Op Code Fetch Cycle

Memory Read/Write Cycle

T2 rise - T3 fall

(1.5 Phi + nw x Phi)

I/O read Cycle

1st Tw rise - T3 fall

(0.5Phi + nw x Phi)

I/O Write Cycle

1st Tw rise - T3 rise

In

w

x Phi)

NMI Acknowledge 1st MC

T2 rise - T3 fall

(1.5 Phi)

INT0 Acknowledge 1st MC

1st Tw rise - T3 fall

(0.50 + nw x Phi

)

BUS RELEASE mode

SLEEP mode

SYSTEM STOP mode

Phi

fall - Phi

fall

(2 Phi or 1 Phi)

Note: nw = the number of Wait States; MC: Machine Cycle