Table 15, Channel 1 transfer mode – Zilog Z80180 User Manual

Page 117

Z8018x

Family MPU User Manual

102

UM005003-0703

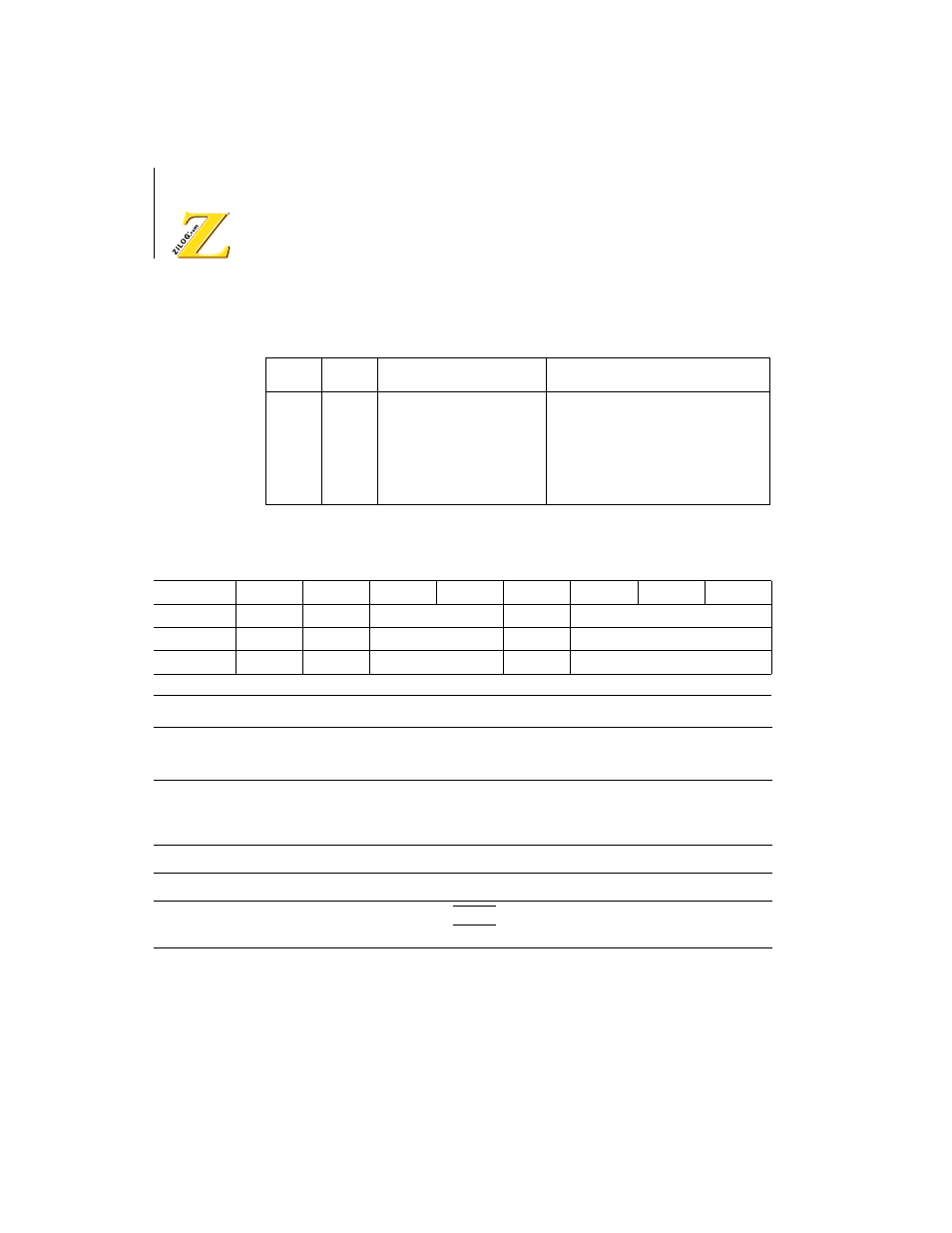

Table 15. Channel 1 Transfer Mode

DIM1 DIM0 Transfer Mode

Address Increment/Decrement

0

0

Memory

to

I/O

MARI +1, IAR1 fixed

0

1

Memory

to

I/O

MARI -1, IAR1 fixed

1

0

I/O

to

Memory

IAR1 fixed, MAR1+1

1

1

I/O

to

Memory

IAR1 fixed, MAR1-1

DMA I/O Address Register Ch. 1 (IAR1B: 2DH) (Z8S180/L180-Class Processor Only)

Bit

7

6

5

4

3

2

1

0

Bit/Field

Reserved

R/W

R/W

R/W

R/W

R/W

R/W

Reset

0

0

0

0

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

Bit

Position Bit/Field

R/W

Value Description

7

R/W

0

1

Alternating Channels

DMA Channels are independent

Toggle between DMA channels for same device

6

R/W

Currently selected DMA channel when Bit 7 = 1

5

–

4

Reserved

R/W

0

Reserved. Must be 0.

3

R/W

0

1

TOUT/DREQ is DREQ In

TOUT/DREQ is TOUT Out