Zilog Z80180 User Manual

Page 140

Z8018x

Family MPU User Manual

UM005003-0703

125

ASCI Control Register A0, 1 (CNTLA0, 1)

Each ASCI channel Control Register A configures the major operating

modes such as receiver/transmitter enable and disable, data format, and

multiprocessor communication mode.

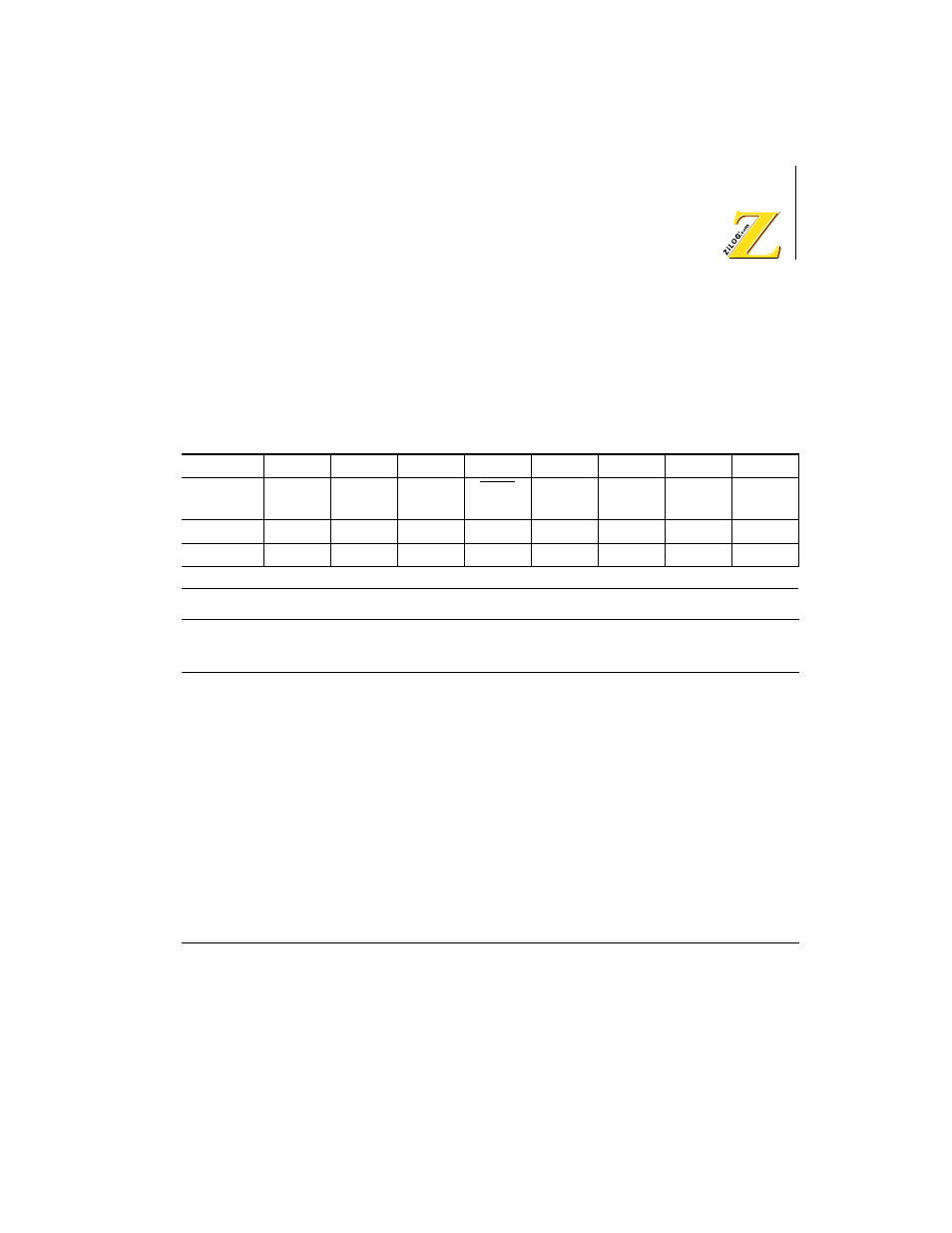

ASCI Control Register A 0 (CNTLA0: 00H)

Bit

7

6

5

4

3

2

1

0

Bit/Field

MPE

RE

TE

RTS0

MPBR/

EFR

MOD2

MOD1

MOD0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset

0 0 0

1

X

0 0 0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

Bit

Position Bit/Field R/W

Value

Description

7

MPE

R/W

Multi-Processor Mode Enable — The ASCI has a

multiprocessor communication mode which utilizes an

extra data bit for selective communication when a number

of processors share a common serial bus. Multiprocessor

data format is selected when the MP bit in CNTLB is set

to 1. If multiprocessor mode is not selected (MP bit in

CNTLB = 0), MPE has no effect. If multiprocessor mode

is selected, MPE enables or disables the wakeup feature

as follows. If MPE is set to 1, only received bytes in

which the MPB (multiprocessor bit) is 1 can affect the

RDRF and error flags. Effectively, other bytes (with MPB

is 0) are ignored by the ASCI. If MPE is reset to 0, all

bytes, regardless of the state of the MPB data bit, affect

the RDRF and error flags.