Zilog Z80180 User Manual

Page 310

Z8018x

Family MPU User Manual

294

UM005003-0703

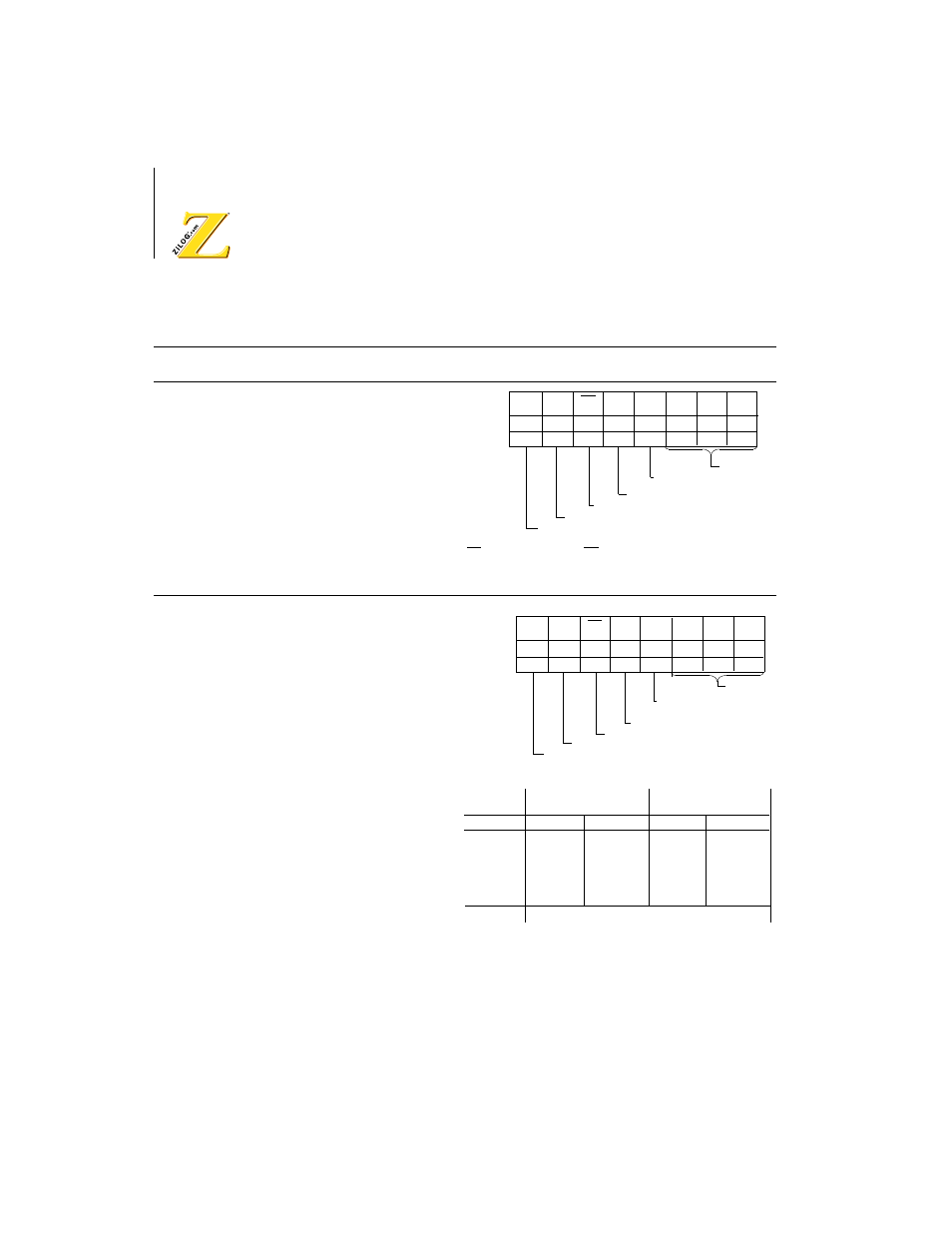

ASCI Control Register B

Channel 0:

CNTLB0 0

2

ASCI Control Register B

Channel 1:

CNTLB1 0

3

Table 57. Internal I/O Registers (Continued)

Register

Mnemonics Address

Remarks

MPBT

MP

CTS/

PS

PEO

DR

SS2

SS1

SS0

bit

during RESET

R/W

0

0

0

*

1

1

1

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Clock Source and

Speed Select

Divide Ratio

Parity Even or Odd

Clear to send/Prescale

Multi Processor

Multi Processor Bit Transmit

* CTS: Depending on the condition 0f CTS Pin.

PS: Cleared to 0.

invalid

MPBT

MP

CTS/

PEO

DR

SS2

SS1

SS0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Clock Source and

Divide Ratio

Clear to Send/Prescale

Multi Processor

Multi Processor Bit Transmit

0

invalid

0

0

0

1

1

1

bit

during RESET

R/W

PS

Speed Select

Parity Even or Odd

General

divide ratio

PS=0

(divide ratio=10)

PS=1

(divide ratio=30)

SS2 1 0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

f ¸

160

¸

¸

¸

¸

¸

¸

f ¸

¸

¸

¸

¸

¸

¸

320

10240

5120

2560

1280

640

f ¸

640

¸

¸

¸

¸

¸

¸

1280

2560

5120

10240

20480

40960

f ¸

480

¸

¸

¸

¸

¸

¸

960

1920

3840

7680

15360

30720

1920

3840

7680

15360

30720

61440

122880

External clock (frequency <

f ¸ 40)

DR=0 (X 16)

DR=1 (X 64)

DR=0 (X 16)

DR=1 (X 64)