Zilog Z80180 User Manual

Page 210

Z8018x

Family MPU User Manual

UM005003-0703

195

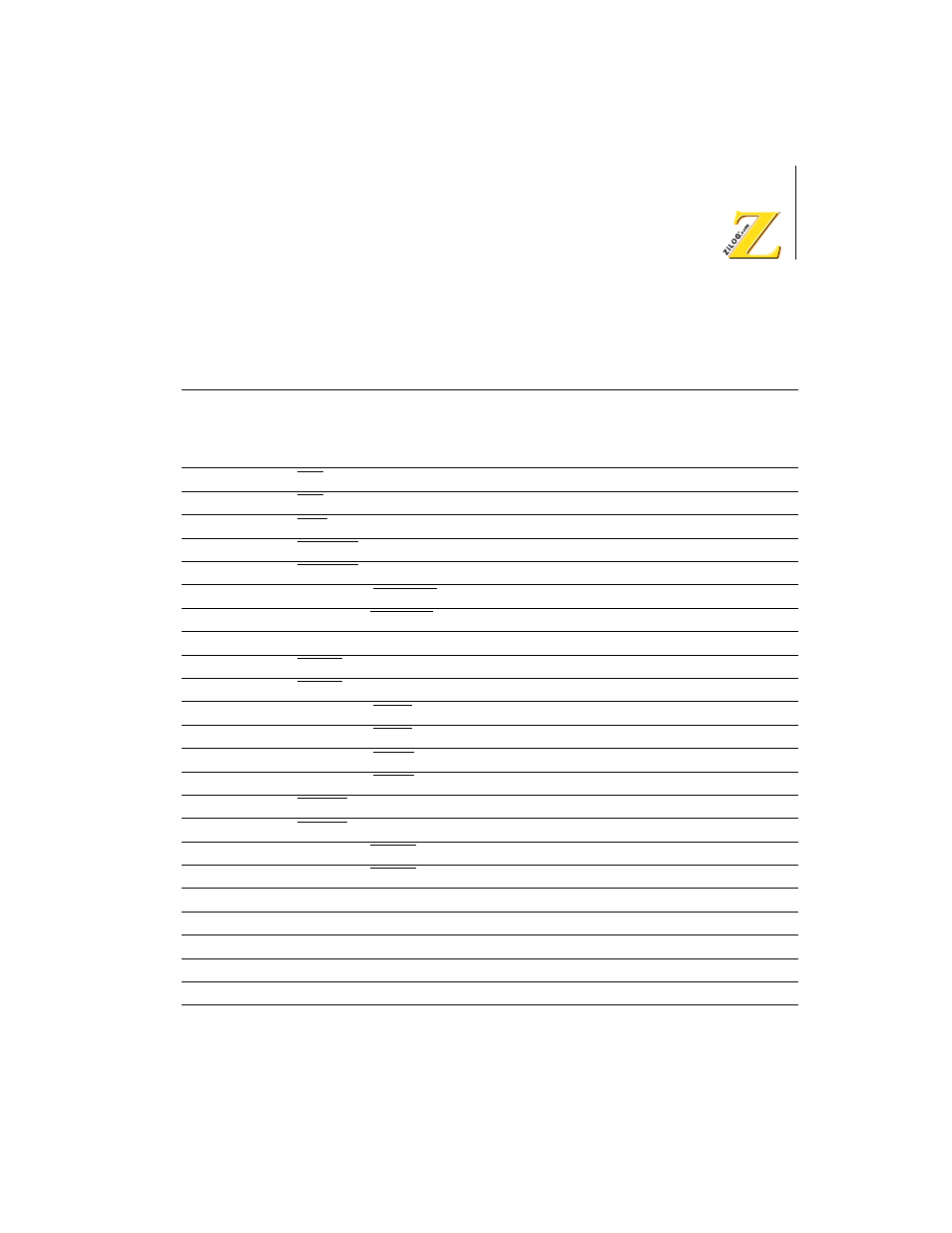

31

t

INTS

INT Set-up Time to PHI Fall

20

—

15

—

ns

32

t

INTH

INT Hold Time from PHI Fall

10

—

10

—

ns

33

t

NMIW

NMI Pulse Width

35

—

25

—

ns

34

t

BRS

BUSREQ Set-up Time to PHI Fall

10

—

10

—

ns

35

t

BRH

BUSREQ Hold Time from PHI Fall 10

—

10

ns

36

t

BAD1

PHI Rise to BUSACK Fall Delay

—

25

—

15

ns

37

t

BAD2

PHI Fall to BUSACK Rise Delay

—

25

—

15

ns

38

t

BZD

PHI Rise to Bus Floating Delay Time —

40

—

30

ns

39

t

MEWH

MREQ Pulse Width (High)

35

—

25

—

ns

40

t

MEWL

MREQ Pulse Width (Low)

35

—

25

—

ns

41

t

RFD1

PHI Rise to RFSH Fall Delay

—

20

—

15

ns

42

t

RFD2

PHI Rise to RFSH Rise Delay

—

20

—

15

ns

43

t

HAD1

PHI Rise to HALT Fall Delay

—

15

—

15

ns

44

t

HAD2

PHI Rise to HALT Rise Delay

—

15

—

15

ns

45

t

DRQS

DREQ1 Set-up Time to PHI Rise

20

—

15

—

ns

46

t

DRQH

DREQ1 Hold Time from PHI Rise

20

—

15

—

ns

47

t

TED1

PHI Fall to TENDi Fall Delay

—

25

—

15

ns

48

t

TED2

PHI Fall to TENDi Rise Delay

—

25

—

15

ns

49

t

ED1

PHI Rise to E Rise Delay

—

30

—

15

ns

50

t

ED2

PHI Fall or Rise to E Fall Delay

—

30

—

15

ns

51

P

WEH

E Pulse Width (High)

25

—

20

—

ns

52

P

WEL

E Pulse Width (Low)

50

—

40

—

ns

53

t

Er

Enable Rise Time

—

10

—

10

ns

Table 31. Z8S180 AC Characteristics (Continued) V

DD

= 5V ±10% or

V

DD

= 3.3V ±10%; 33-MHz Characteristics Apply Only to 5V

Operation

No.

Symbol Item

Z8S180—20

MHz

Z8S180—33

MHz

Unit

Min

Max

Min

Max