Table 11, Dram refresh intervals – Zilog Z80180 User Manual

Page 104

Z8018x

Family MPU User Manual

UM005003-0703

89

Refresh Control And RESET

After RESET, based on the initialized value of RCR, refresh cycles occur

with an interval of ten clock cycles and are three clock cycles in duration.

Dynamic Ram Refresh Operation Notes

1. Refresh Cycle insertion is stopped when the CPU is in the following

states:

–

During RESET

–

When the bus is released in response to BUSREQ

–

During SLEEP mode

–

During Wait States

2. Refresh cycles are suppressed when the bus is released in response to

BUSREQ. However, the refresh timer continues to operate. Thus, the

time at which the first refresh cycle occurs after the Z8X180 re-

acquires the bus depends on the refresh timer and has no timing

relationship with the bus exchange.

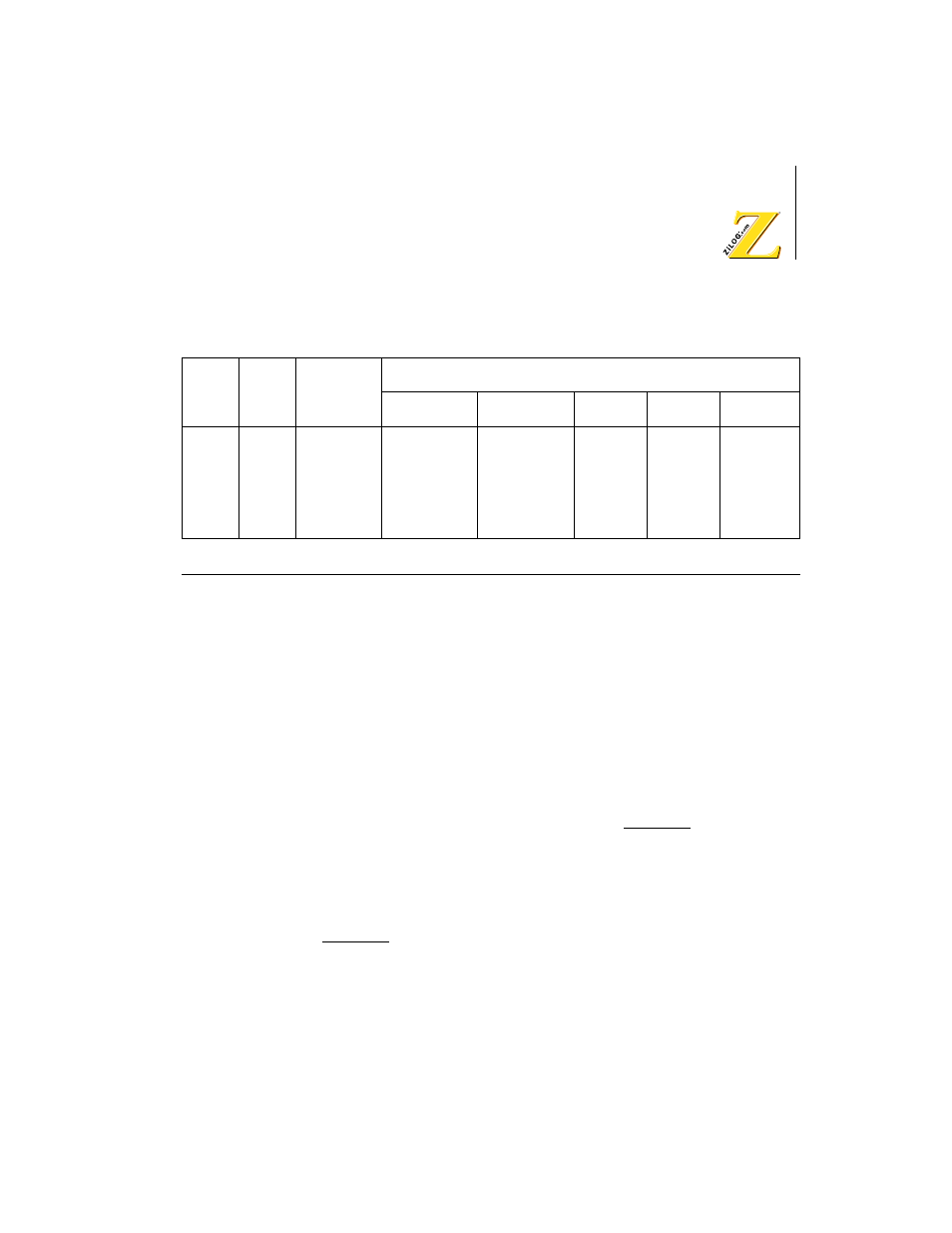

Table 11. DRAM Refresh Intervals

CYC1 CYC0

Insertion

Interval

Time Interval

10 MHz

8 MHz

6 MHz

4 MHz

2.5 MHz

0

0

10 states

(1.0

m

s)*

(1.25

m

s)*

1.66

m

s

2.5

m

s

4.0

m

s

0

1

20 states

(2.0

m

s)*

(2.5

m

s)*

3.3

m

s

5.0

m

s

8.0

m

s

1

0

40 states

(4.0

m

s)*

(5.0

m

s)*

6.8

m

s

10.0

m

s

16.0

m

s

1

1

80 states

(8.0

m

s)*

(10.0

m

s)*

13.3

m

s

20.0

m

s

32.0

m

s

* Calculated interval