Table 1, Status summary – Zilog Z80180 User Manual

Page 25

Z8018x

Family MPU User Manual

10

UM005003-0703

RTS0. Request to Send 0 (Output, Active Low). This output is a

programmable modem control signal for ASCI channel 0.

RXA0, RXA1. Receive Data 0 and 1 (Inputs, Active High). These signals

are the receive data to the ASCI channels.

RXS. Clocked Serial Receive Data (Input, Active High). This line is the

receiver data for the CSIO channel. RXS is multiplexed with the CTS1

signal for ASCI channel 1.

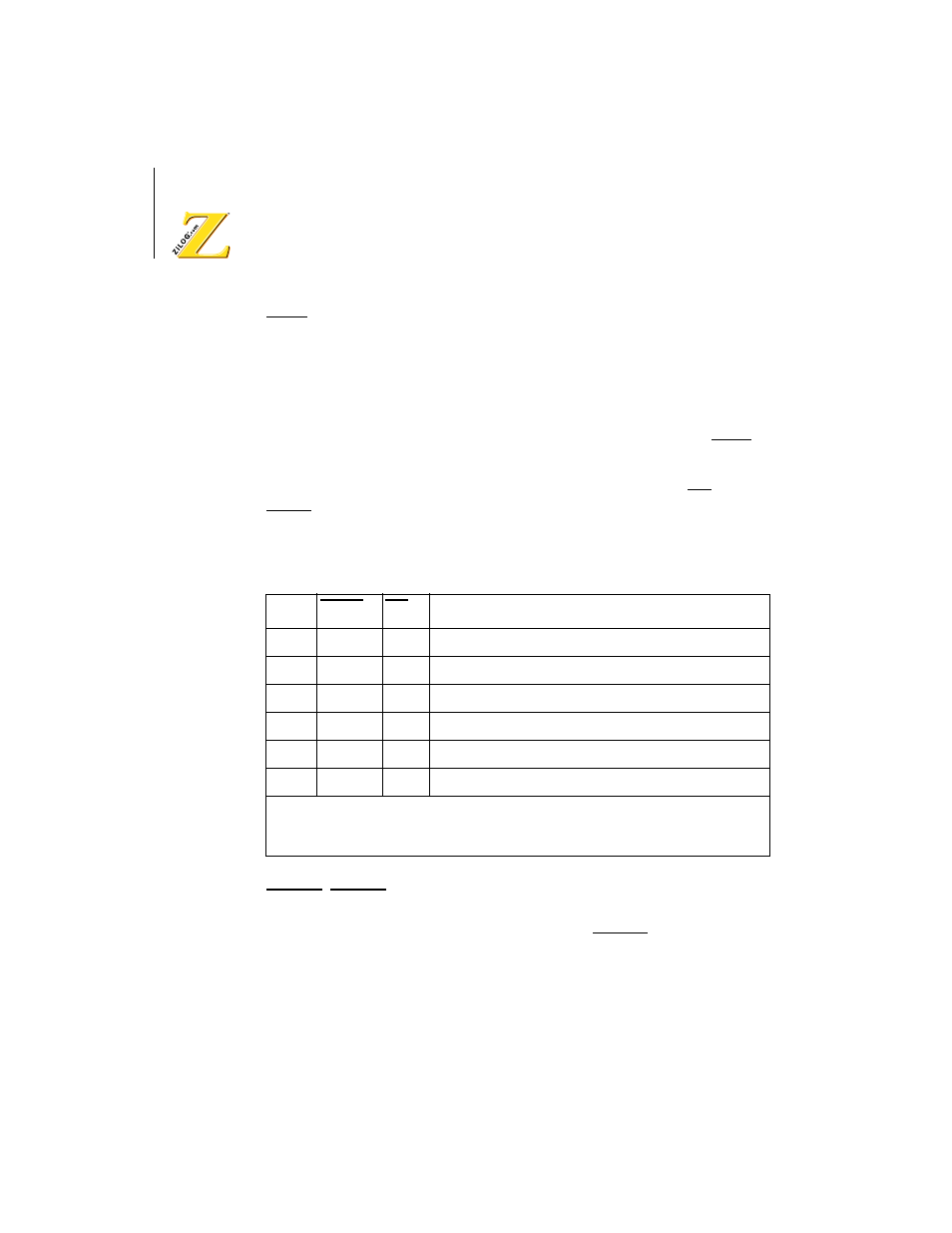

ST. Status (Output, Active High). This signal is used with the M1 and

HALT output to decode the status of the CPU machine cycle. Table 1

provides status summary.

TEND0, TEND1. Transfer End 0 and 1 (Outputs, Active Low). This

output is asserted active during the last write cycle of a DMA operation. It

is used to indicate the end of the block transfer. TEND0 in multiplexed

with CKA1.

TEST. Test (Output, not on DIP version). This pin is for test and must be

left open.

Table 1.

Status Summary

ST

HALT

M1

Operation

0

1

0

CPU operation (1st Op Code fetch)

1

1

0

CPU operation (2nd Op Code and 3rd Op Code fetch)

1

1

1

CPU operation (MC

2

except for Op Code fetch)

0

X

1

1

DMA operation

0

0

0

HALT mode

1

0

1

SLEEP mode (including SYSTEM STOP mode)

1. X = Don't care

2. MC = Machine cycle