Zilog Z80180 User Manual

Page 152

Z8018x

Family MPU User Manual

UM005003-0703

137

Each ASCI channel control register B configures multiprocessor mode,

parity and baud rate selection.

2

Break

Feature

Enable

R/W

0

1

Break Feature Enable On

Break Feature Enable Off

1

Break

Detect

(RO)

R/W

0

1

Break Detect On

Break Detect Off

0

Send

Break

R/W

0

1

Normal Xmit

Drive TXA Low

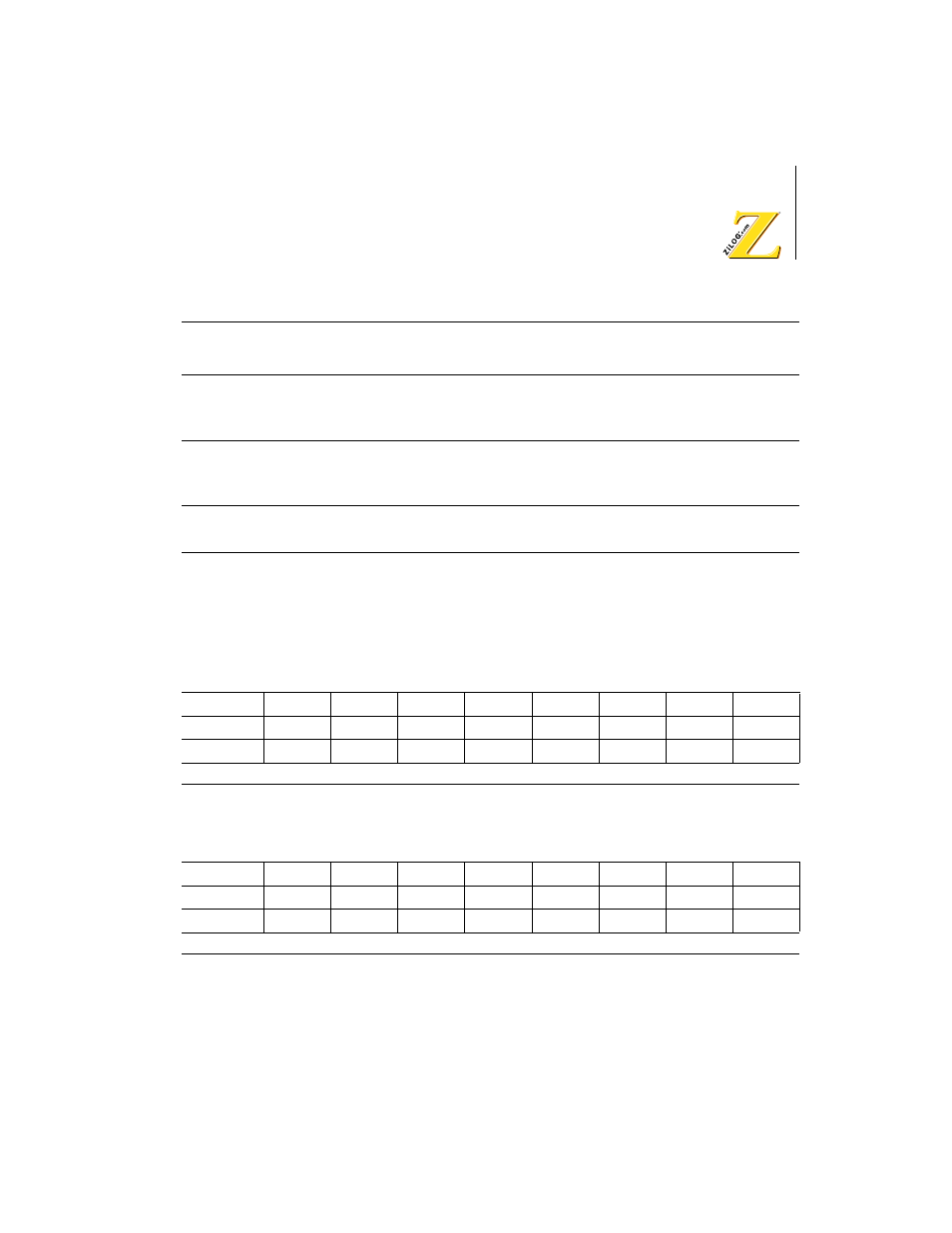

ASCI0 Time Constant Low Register (I/O Address: 1AH) (Z8S180/L180-Class Processors

Only)

Bit

7

6

5

4

3

2

1

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset

0

0

0

0

0

0

0

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

ASCI0 Time Constant High Register (I/O Address: 1BH) (Z8S180/L180-Class Processors

Only)

Bit

7

6

5

4

3

2

1

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset

0

0

0

0

0

0

0

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

Bit

Position Bit/Field

R/W

Value Description