Table 18, Divide ratio – Zilog Z80180 User Manual

Page 149

Z8018x

Family MPU User Manual

134

UM005003-0703

pins are initialized as ASCI data clock inputs. If SS2, SS1 and SS0 are

reprogrammed (any other value than SS2, SS1, SS0 =

1

) these pins

become ASCI data clock inputs. However, if DMAC channel 0 is

configured to perform memory to/from I/O (and memory mapped I/O)

transfers the CKA0/DREQ0 pin reverts to DMA control signals

regardless of SS2, SS1, SS0 programming.

Also, if the CKA1D bit in the CNTLA register is

1

, then the CKA1/

TEND0 reverts to the DMA Control output function regardless of SS2,

SS1 and SS0 programming. Final data clock rates are based on CTS/PS

(prescale), DR, SS2, SS1, SS0 and the Z8X180 system clock frequency

(Reference Table 19).

Each ASCI channel control register B configures multiprocessor mode,

parity and baud rate selection.

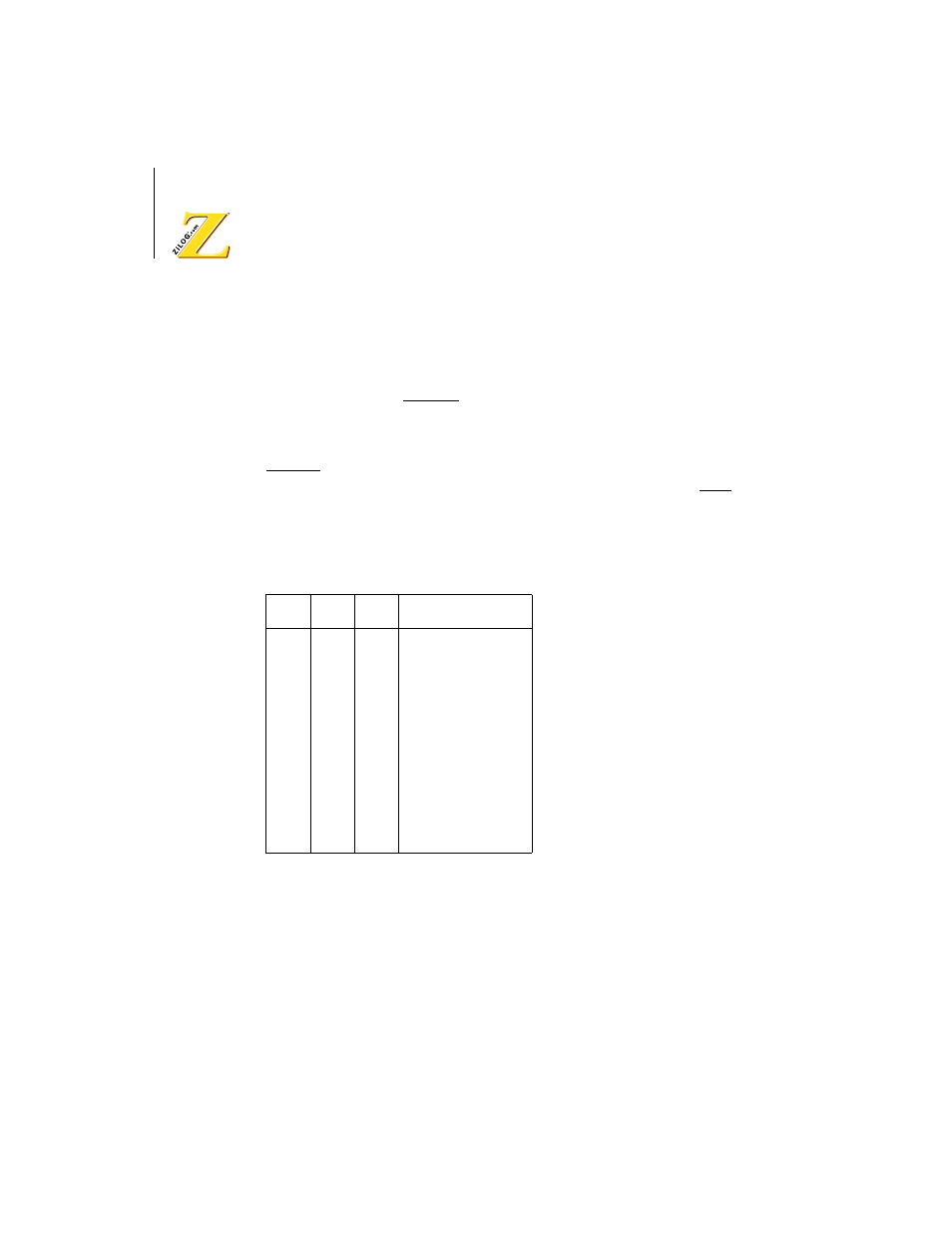

Table 18. Divide Ratio

SS2

SS1

SS0

Divide Ratio

0

0

0

¸

1

0

0

1

¸

2

0

1

0

¸

4

0

1

1

¸

8

1

0

0

¸

16

1

0

1

¸

32

1

1

0

¸

64

1

1

1

external clock