Figure 47. cpu operation and dma operation dreq0, Is programmed for level-sense, Z8018x family mpu user manual – Zilog Z80180 User Manual

Page 122: Or tw)

Z8018x

Family MPU User Manual

UM005003-0703

107

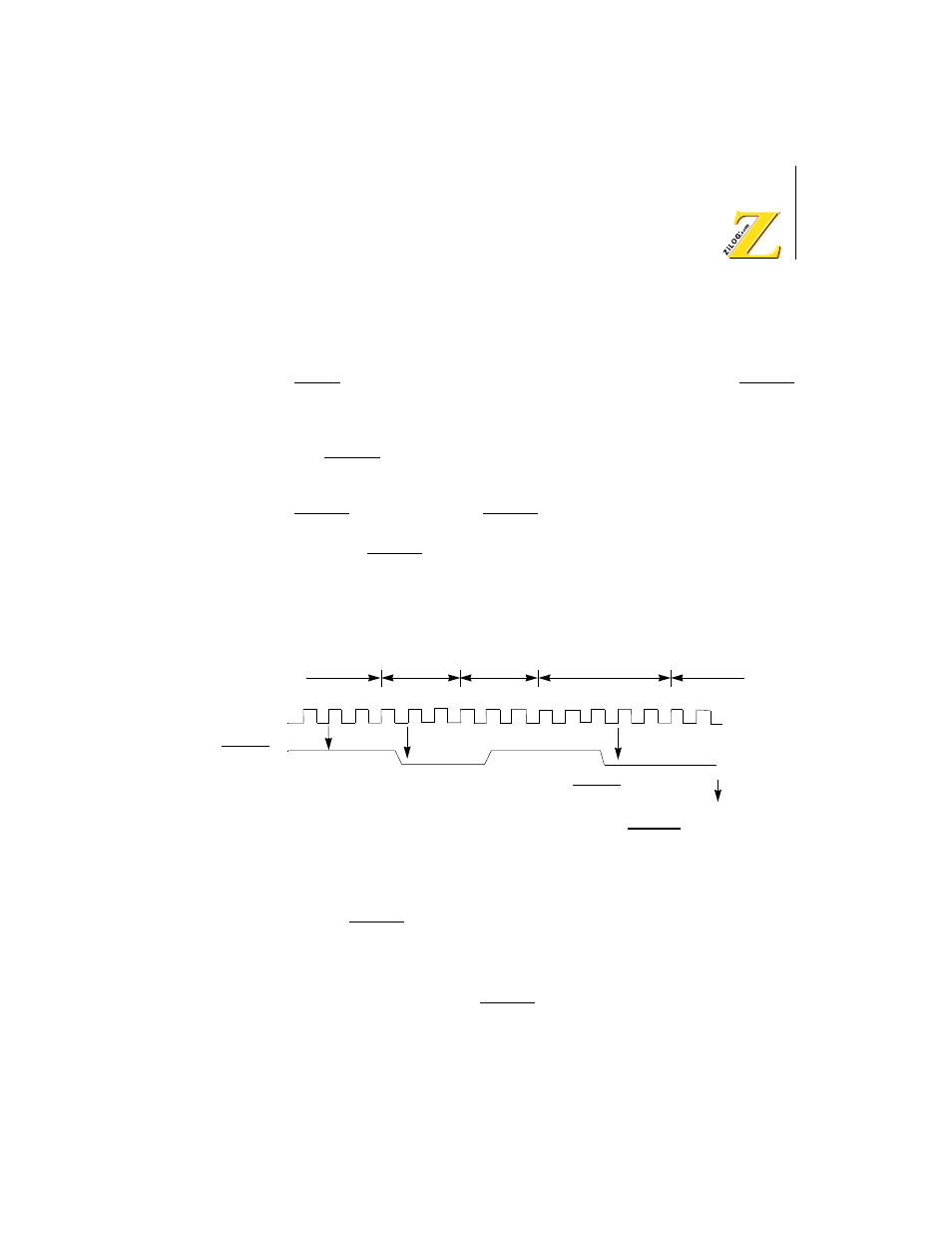

Memory to I/O (Memory Mapped I/O) — Channel 0

For memory to/from I/O (and memory to/from memory mapped I/O) the

DREQ0 input is used to time the DMA transfers. In addition, the TEND0

(Transfer End) output is used to indicate the last (byte count register

BCR0 =

00H

) transfer.

The DREQ0 input can be programmed as level- or edge-sensitive.

When level-sense is programmed, the DMA operation begins when

DREQ0 is sampled Low. If DREQ0 is sampled High, after the next DMA

byte transfer, control is relinquished to the Z8X180 CPU. As illustrated in

Figure 47, DREQ0 is sampled at the rising edge of the clock cycle prior to

T3, (that is, either T2

or Tw).

Figure 47. CPU Operation and DMA Operation DREQ0 is Programmed

for Level-Sense

When edge-sense is programmed, DMA operation begins at the falling

edge of DREQ0 If another falling edge is detected before the rising edge

of the clock prior to T3 during DMA write cycle (that is T2 or Tw), the

DMAC continues operating. If an edge is not detected, the CPU is given

control after the current byte DMA transfer completes. The CPU

continues operating until a DREQ0 falling edge is detected before the

Tw

T1

T2

T3

Tw

Tw Tw

T1

T1

T1

T2

T2

T2

T3

T3

T3

DMA

CPU

DMA

DMA

**

**

**

** DREQ0 is sampled at

DREQ0

Phi

Write

Cycle

Machine

Cycle

Read

Cycle

Write

Cycle (I/O)