And interrupt acknowledge cycle, Figure 68. e clock timing in bus release mode, Z8018x family mpu user manual – Zilog Z80180 User Manual

Page 182

Z8018x

Family MPU User Manual

UM005003-0703

167

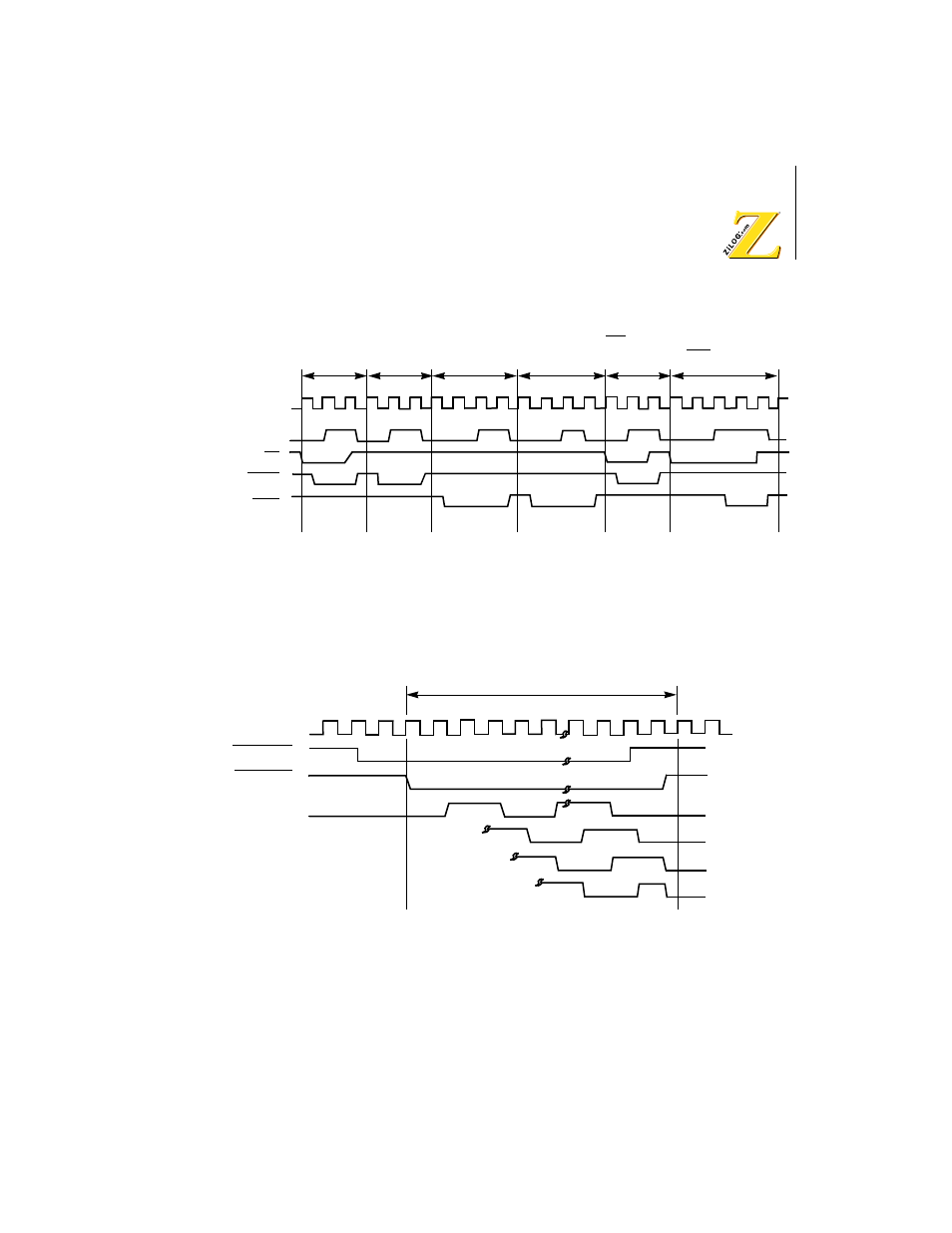

Figure 67. E Clock Timing Diagram (During Read/Write Cycle and

Interrupt Acknowledge Cycle

Figure 68. E Clock Timing in BUS RELEASE Mode

Op Code

Fetch Cycle

M1

MREQ

Phi

IORQ

Memory Read/

Write Cycle

I/O Write Cycle

NMI

Acknowledge

1st MC

INT0 Acknowledge

1st MC

I/O Read Cycle

NOTE : MC = Machine Cycle

* Two wait states are automatically inserted

E

T1 T2 T3

Tw*

T1

T1

T1

T1

T1

T2

T2

T2

T2

T2

T3

T3

T3

T3

T3

Tw

Tw*

Phi

BUSREQ

BUSACK

E

Last

state

TX

TX

TX TX

BUS RELEASE mode

E

E

E