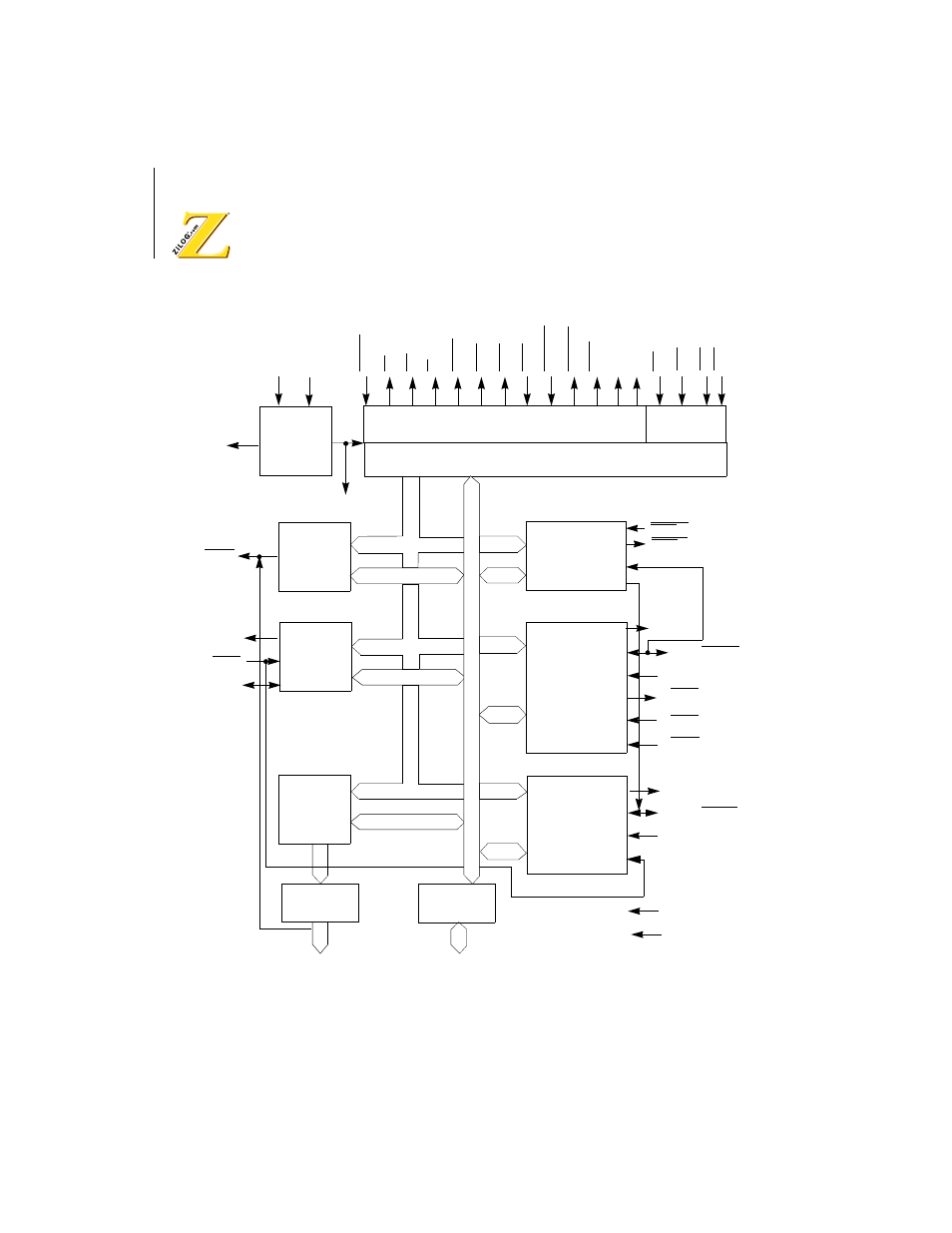

Figure 4, Z80180/z8s180/z8l180 block diagram – Zilog Z80180 User Manual

Page 21

Z8018x

Family MPU User Manual

6

UM005003-0703

Figure 4.

Z80180/Z8S180/Z8L180 Block Diagram

MMU

Address

Buffer

Data

Buffer

A0

–

A19

D0

–

DF

Asynchronous

SCI

(Channel 0)

CPU

DMACs

(2)

DREQ1

TEND1

CKA0/DREQ0

Interrupt

Bus State Control

Asynchronous

SCI

(channel 1)

R

ESET

RD

WR

MI

MR

EQ

IO

RQ

HA

LT

WA

IT

BU

SR

EQ

BU

SAC

K

RF

S

H

ST

E

NMI

IN

T

0

IN

T

1

IN

T

2

RXA0

RTS0

CTS0

DCD0

TXA0

TXA1

CKA1/TEND0

RXA1

V

CC

V

SS

16-bit

Programmable

Reload

Timers

TXS

RXS/CTS1

CKS

A18/TOUT

Clocked

Serial I/O

Port

Timing

Generator

Ad

dr

e

ss Bus

(1

6-

b

it)

XT

A

L

EX

T

A

L

Phi

D

a

ta

B

u

s (8

-b

it)