Zilog Z80180 User Manual

Page 85

Z8018x

Family MPU User Manual

70

UM005003-0703

TRAP Interrupt

The Z8X180 generates a non-maskable (not affected by the state of IEF1)

TRAP interrupt when an undefined Op Code fetch occurs. This feature

can be used to increase software reliability, implement an extended

instruction set, or both. TRAP may occur during Op Code fetch cycles

and also if an undefined Op Code is fetched during the interrupt

acknowledge cycle for INT0 when Mode 0 is used.

When a TRAP interrupt occurs the Z8X180 operates as follows:

1. The TRAP bit in the Interrupt TRAP/Control (ITC) register is set to

1

.

2. The current PC (Program Counter) value, reflecting location of the

undefined Op Code, is saved on the stack.

3. The Z8X180 vectors to logical address 0. Note that if logical address

0000H

is mapped to physical address

00000H

. the vector is the same

as for RESET. In this case, testing the TRAP bit in ITC reveals

whether the restart at physical address

00000H

was caused by

RESET or TRAP.

The state of the UFO (Undefined Fetch Object) bit in ITC allows TRAP

manipulation software to correctly adjust the stacked PC, depending on

whether the second or third byte of the Op Code generated the TRAP. If

UFO is

0

, the starting address of the invalid instruction is equal to the

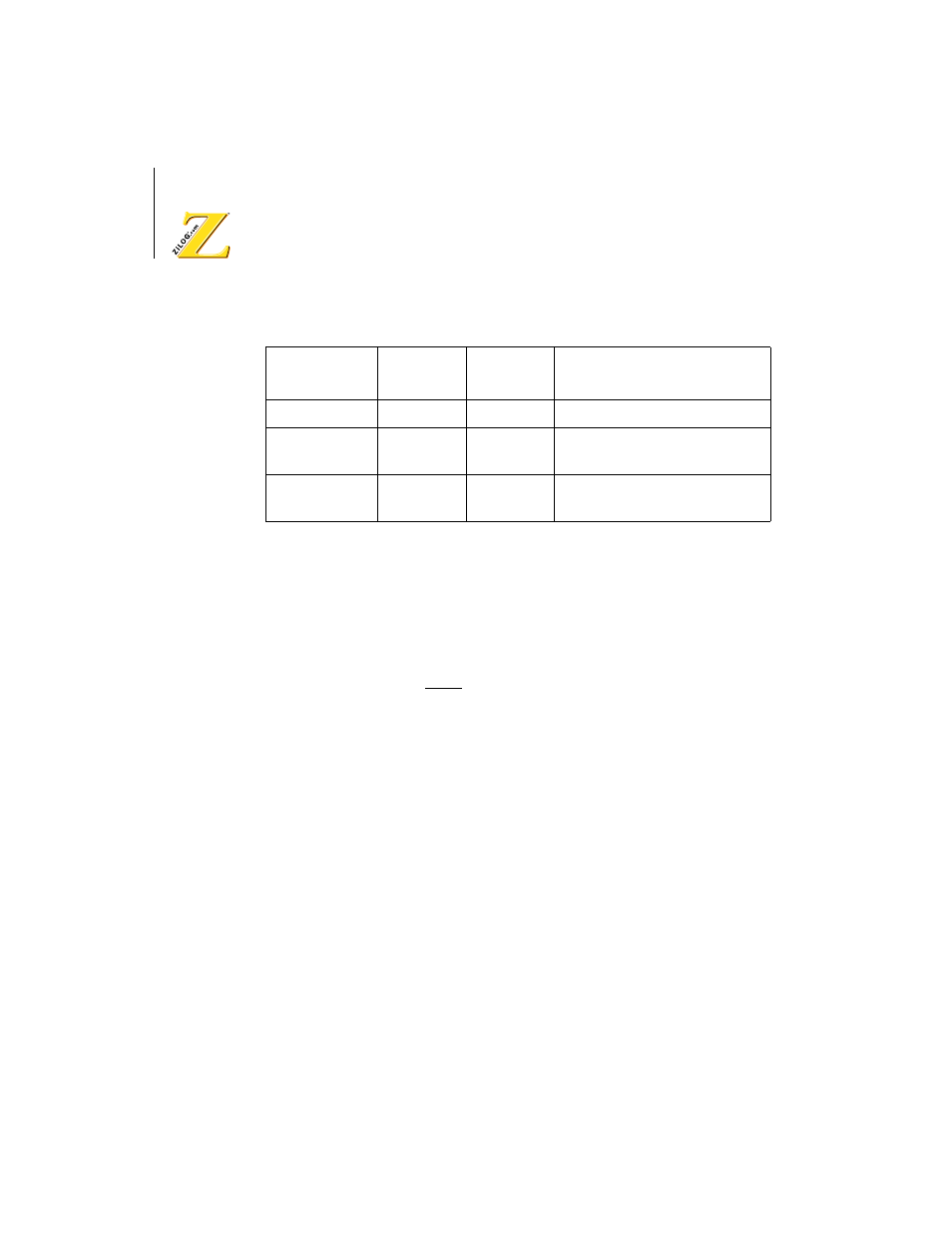

DI

0

0

LD A, I

not affected not affected Transfers the contents of IEF1 to

P/V

LID A, R

not affected not affected Transfers the contents of IEF1 to

P/V

Table 8.

State of IEF1 and IEF2 (Continued)

CPU

Operation

IEF1

IEF2

REMARKS