Zilog Z80180 User Manual

Page 209

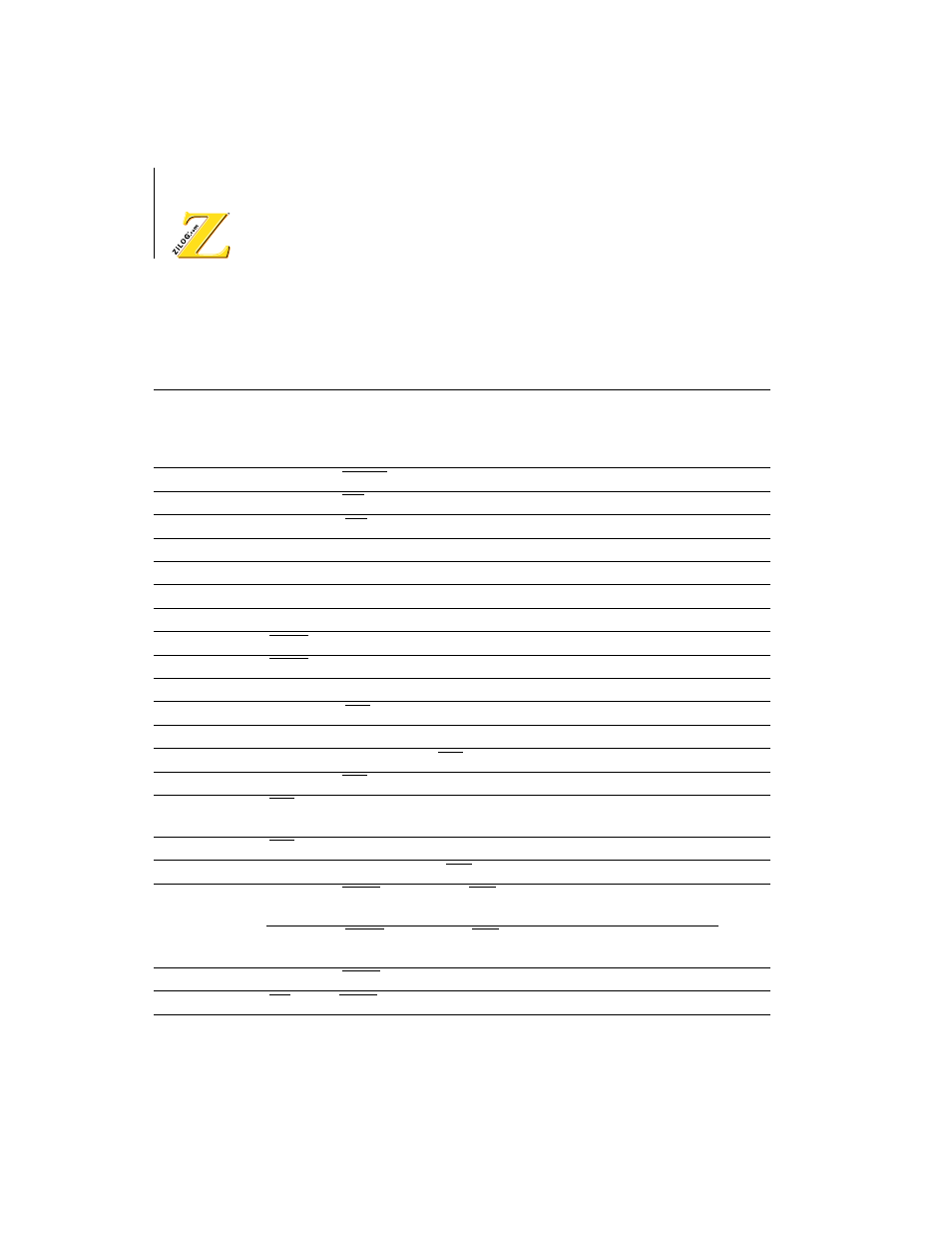

Z8018x

Family MPU User Manual

194

UM005003-0703

12

t

MED2

PHI Fall to MREQ Rise Delay

—

25

—

15

ns

13

t

RDD2

PHI Fall to RD Rise Delay

—

25

—

15

ns

14

t

M1D2

PHI Rise to M1 Rise Delay

—

40

—

15

ns

15

t

DRS

Data Read Set-up Time

10

—

5

—

ns

16

t

DRH

Data Read Hold Time

0

—

0

—

ns

17

t

STD1

PHI Fall to ST Fall Delay

—

30

—

15

ns

18

t

STD2

PHI Fall to ST Rise Delay

—

30

—

15

ns

19

t

WS

WAIT Set-up Time to PHI Fall

15

—

10

—

ns

20

t

WH

WAIT Hold Time from PHI Fall

10

—

5

—

ns

21

t

WDZ

PHI Rise to Data Float Delay

—

35

—

20

ns

22

t

WRD1

PHI Rise to WR Fall Delay

—

25

—

15

ns

23

t

WDD

PHI Fall to Write Data Delay Time

—

25

—

15

ns

24

t

WDS

Write Data Set-up Time to WR Fall

10

—

10

—

ns

25

t

WRD2

PHI Fall to WR Rise Delay

—

25

—

15

ns

26

t

WRP

WR Pulse Width (Memory Write

Cycle)

80

—

45

—

ns

26a

WR Pulse Width (I/O Write Cycle)

150

—

70

—

ns

27

t

WDH

Write Data Hold Time from WR Rise 10

—

5

—

ns

28

t

IOD1

PHI Fall to IORQ Fall Delay

IOC

= 1

—

25

—

15

ns

PHI Rise to IORQ Fall Delay

IOC

= 0

—

25

—

15

29

t

IOD2

PHI Fall to IORQ Rise Delay

—

25

—

15

ns

30

t

IOD3

M1 Fall to IORQ Fall Delay

125

—

80

—

ns

Table 31. Z8S180 AC Characteristics (Continued) V

DD

= 5V ±10% or

V

DD

= 3.3V ±10%; 33-MHz Characteristics Apply Only to 5V

Operation

No.

Symbol Item

Z8S180—20

MHz

Z8S180—33

MHz

Unit

Min

Max

Min

Max