Zilog Z80180 User Manual

Page 116

Z8018x

Family MPU User Manual

UM005003-0703

101

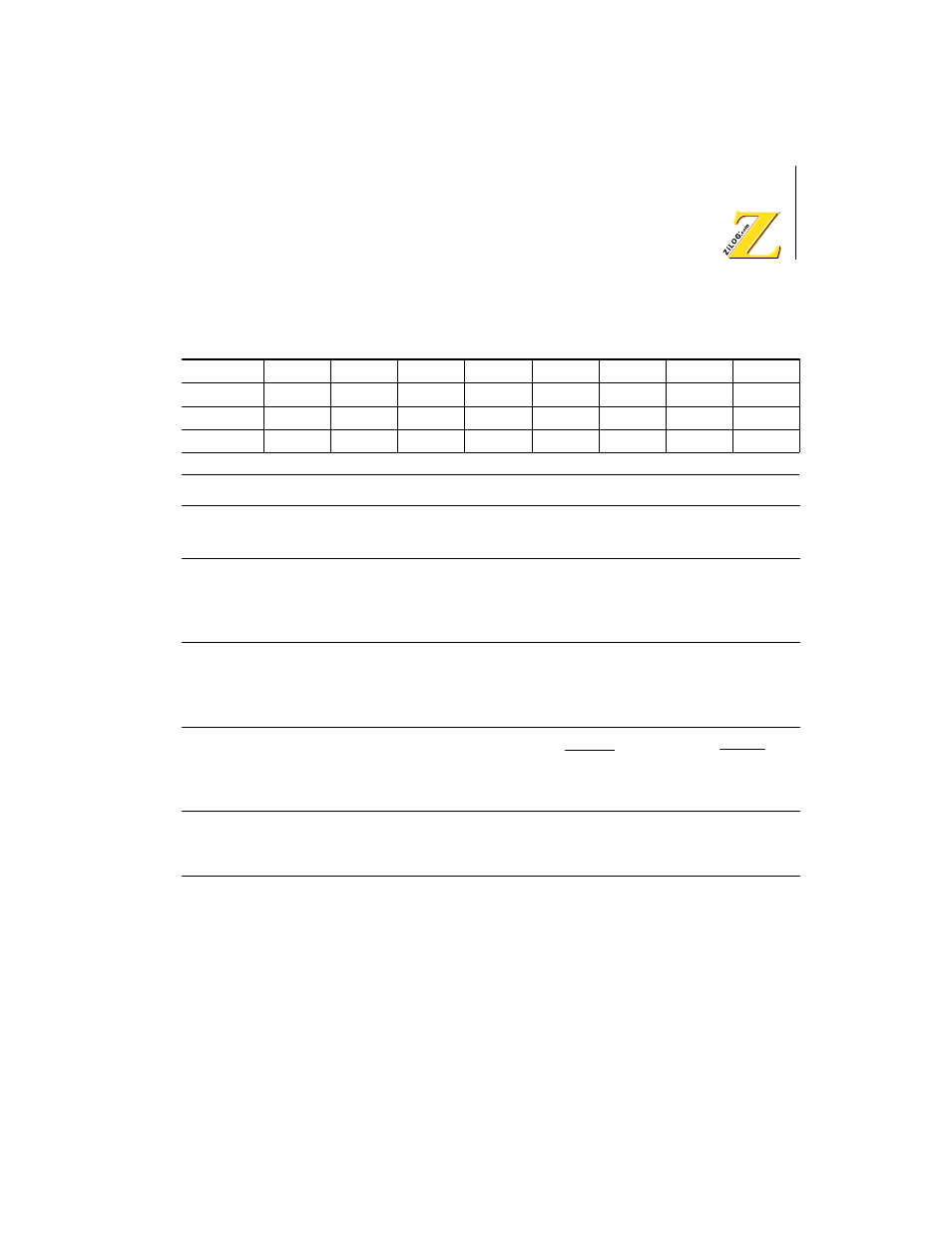

DMA/WAIT Control Register (DCNTL: 32H)

Bit

7

6

5

4

3

2

1

0

Bit/Field

MWI1

MWI0

IWI1

IWI0

DMS1

DMS0

DIM1

DIM0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset

0

0

0

0

0

0

0

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

Bit

Position Bit/Field R/W

Value

Description

7

–

6

MWI1

–

0 R/W

Memory Wait Insertion —Specifies the number of wait

states introduced into CPU or DMAC memory access

cycles. MWI1 and MWI0 are set to 1 during RESET. See

section on Wait State Generator for details.

5

–

4

IWI1

–

0

R/W

Wait Insertion — Specifies the number of Wait States

introduced into CPU or DMAC I/O access cycles. IWI1

and IWI0 are set to 1 during RESET. See section on Wait

State Generator for details.

3

–

2

DMS1

–

0 R/W

DMA Request Sense — Specifies the DMA request

sense for channel 0 (DREQ0) and channel 1 (

DREQ

1)

respectively. When reset to 0, the input is level-sense.

When set to 1, the input is edge-sense.

1

–

0

DIM1

–

0 R/W

DMA Channel 1 I/O and Memory Mode — Specifies

the source/destination and address modifier for channel 1

memory to/from I/O transfer modes. Reference Table 15.