Zilog Z80180 User Manual

Page 134

Z8018x

Family MPU User Manual

UM005003-0703

119

ASCI Receive Shift Register 0,1(RSR0, 1)

This register receives data shifted in on the RXA pin. When full, data is

automatically transferred to the ASCI Receive Data Register (RDR) if it

is empty. If RSR is not empty when the next incoming data byte is shifted

in, an overrun error occurs. The RSR is not program-accessible.

ASCI Receive Data Register 0,1 (RDR0, 1: I/O Address =

08H

,

09H

)

When a complete incoming data byte is assembled in RSR, it is

automatically transferred to the RDR if RDR is empty. The next incoming

data byte can be shifted into RSR while RDR contains the previous

received data byte. Thus, the ASCI receiver on Z80180 is double-

buffered.

\

On the Z8S180 and Z8L180-class processors are quadruple buffered. The

ASCI Receive Data Register is a read-only register. However, if RDRF =

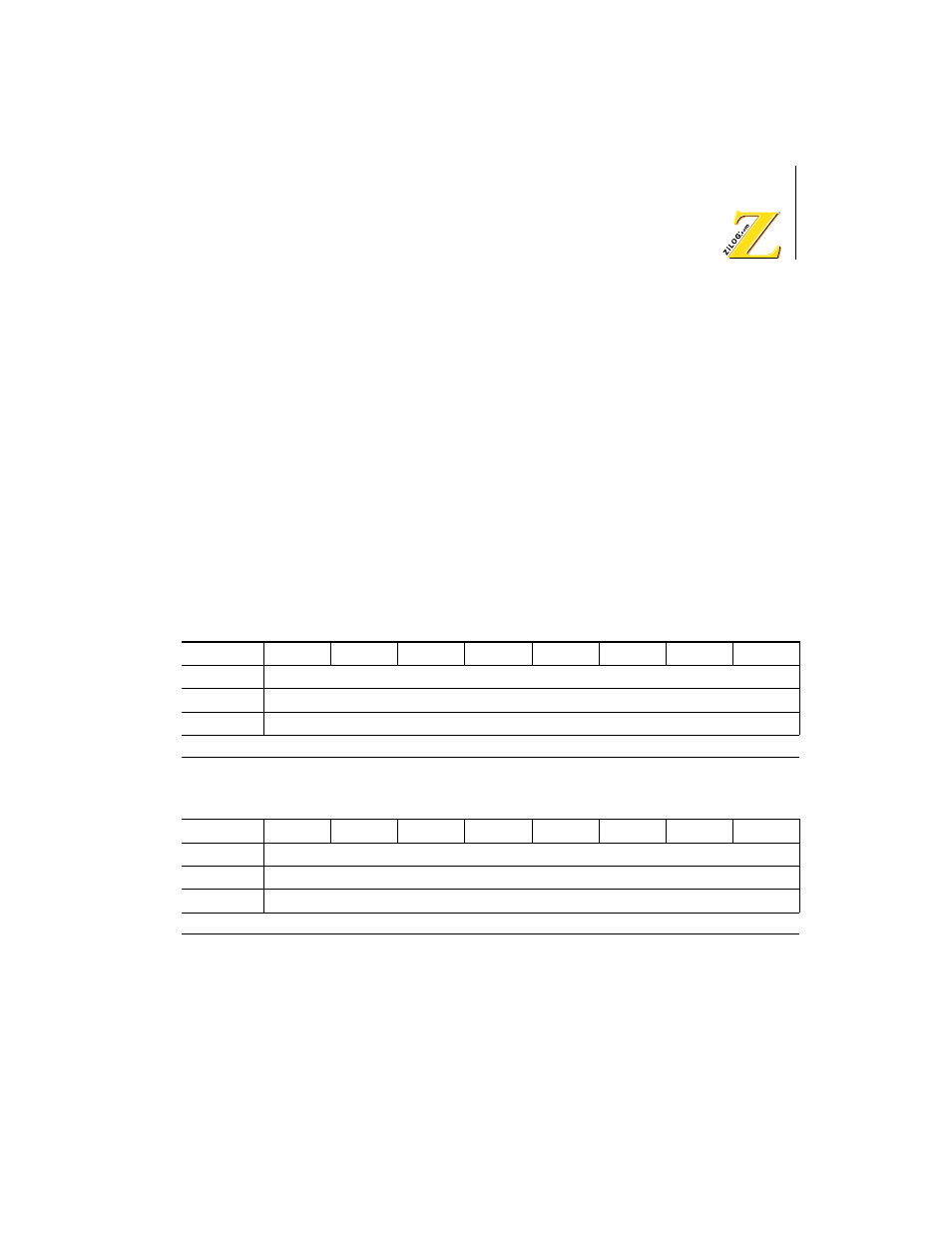

ASCI Receive Data Register Ch. 0 (RDR0: 08H)

Bit

7

6

5

4

3

2

1

0

Bit/Field

ASCI Receive Channel 0

R/W

R/W

Reset

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

ASCI Receive Data Register Ch. 1 (RDR1: 09H)

Bit

7

6

5

4

3

2

1

0

Bit/Field

ASCI Receive Channel 1

R/W

R/W

Reset

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable