Wait state generator – Zilog Z80180 User Manual

Page 42

Z8018x

Family MPU User Manual

UM005003-0703

27

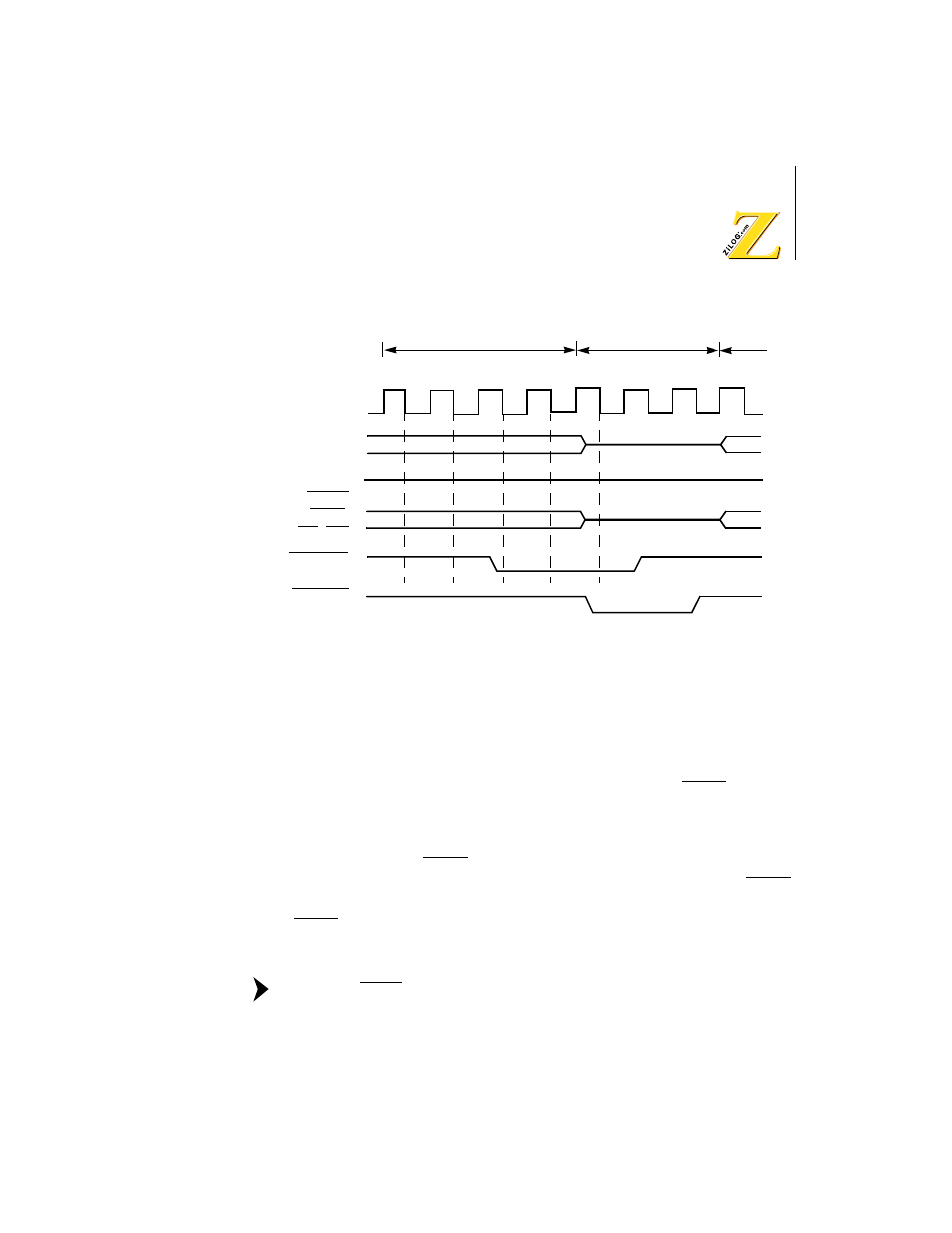

Figure 17. Bus Exchange Timing During CPU Internal Operation

Wait State Generator

To ease interfacing with slow memory and I/O devices, the Z8X180 uses

Wait States (TW) to extend bus cycle timing. A Wait State(s) is inserted

based on the combined (logical OR) state of the external WAIT input and

an internal programmable wait state (TW) generator. Wait States (TW)

can be inserted in both CPU execution and DMA transfer cycles.

When the external WAIT input is asserted Low, Wait State(s) (TW) are

inserted between T2 and T3 to extend the bus cycle duration. The WAIT

input is sampled at the falling edge of the system clock in T2 or TW. If the

WAIT input is asserted Low at the falling edge of the system clock in TW,

another TW is inserted into the bus cycle.

WAIT input transitions must meet specified setup and hold

times. This specification can easily be accomplished by

Phi

A0

–

A19

RD, WR

D0

–

D7

MREQ

IORQ

BUSREQ

BUSACK

CPU Internal Operation

Bus Release Cycle CPU Cycle

T1

T1

T1

TX

T1

TX

T1

TX

Note: