Interrupts, Table 52, Z8018x family mpu user manual – Zilog Z80180 User Manual

Page 295

Z8018x

Family MPU User Manual

UM005003-0703

279

INTERRUPTS

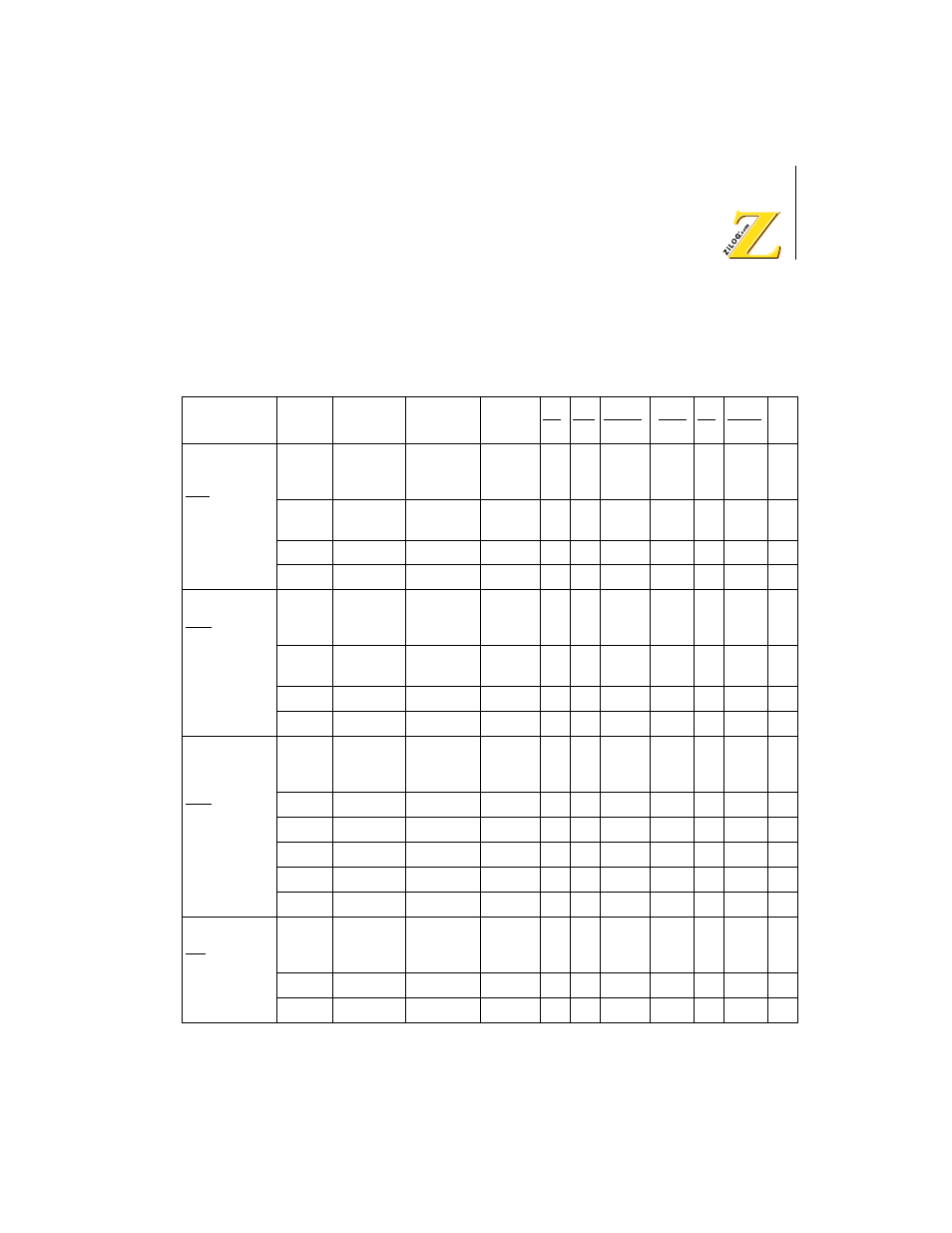

Table 52. Interrupts

Instruction

Machine

Cycle

States

Address

Data

RD WR MREQ IORQ M1 HALT ST

NMI

MC1

T1T2T3

Next Op

Code

Address (PC)

0

1

0

1

0

1

0

MC2

~MC3

T1T1

*

Z

1

1

1

1

1

1

1

MC4

T1T2T3

SP-1

PCH

1

0

0

1

1

1

1

MC5

T1T2T3

SP-2

PCL

1

0

0

1

1

1

1

INT0 Mode 0

(RST Inserted)

MC1

T1T2TW

TWT3

Next Op

Code

Address

1st (PC)

Op Code

1

1

1

0

0

1

0

MC2

~MC3

T1T1

*

Z

1

1

1

1

1

1

1

MC4

T1T2T3

SP-1

PCH

1

0

0

1

1

1

1

MC5

T1T2T3

SP-2

PCL

1

0

0

1

1

1

1

INT0 Mode 0

(Call

Inserted)

MC1

T1T2Tw

TWT3

Next Op

Code

Address (PC)

1st

Op Code

1

1

1

0

0

1

0

MC2

T1T2T3

PC

n

0

1

0

1

1

1

1

MC3

T1T2T3

PC+1

m

0

1

0

1

1

1

1

MC4

Ti

*

Z

1

1

1

1

1

1

1

MC5

T1T2T3

SP-1

PC+2(H)

1

0

0

1

1

1

1

MC6

T1T2T3

SP-2

PC+2(L)

1

0

0

1

1

1

1

INT0 Mode 1

MC1

T1T2TW

TWT3

Next

Op Code

Address (PC)

1

1

1

0

0

1

0

MC2

T1T2T3

SP-1

PCH

1

0

0

1

1

1

1

MC3

T1T2T3

SP-2

PCL

1

0

0

1

1

1

1