Zilog Z80180 User Manual

Page 174

Z8018x

Family MPU User Manual

UM005003-0703

159

Timer Reload Register (RLDR: I/O Address = CH0: 0EH,

0FH, CHI, 16H, 17H)

PRT0 and PRT1 each contain 16-bit Timer Reload Registers (RLDR).

RLDR0 and RLDR1 are each accessed as low and high byte registers

(RLDR0H, RLDR0L and RLDR1H, RLDR1L). During RESET, RLDR0

and RLDR1 are set to

FFFFH

When the TMDR counts down to

0

, it is automatically reloaded with the

contents of RLDR.

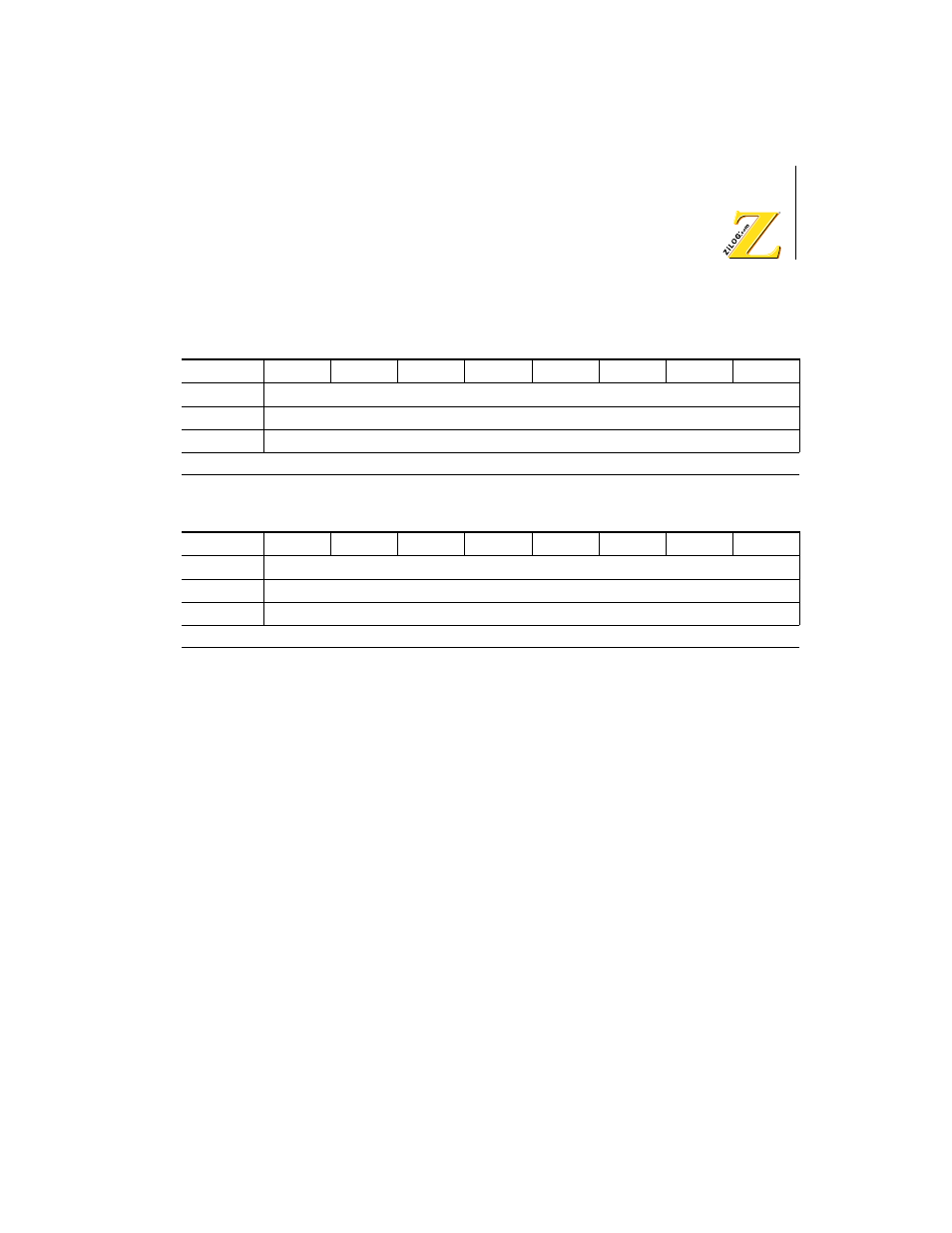

Timer Data Register 0L (TMDR0L: 0CH)

Bit

7

6

5

4

3

2

1

0

Bit/Field

Timer Data

R/W

R/W

Reset

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

Timer Data Register 0H (TMDR0H: 0DH)

Bit

7

6

5

4

3

2

1

0

Bit/Field

Timer Data

R/W

R/W

Reset

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable