Table 16, Dma transfer request – Zilog Z80180 User Manual

Page 125

Z8018x

Family MPU User Manual

110

UM005003-0703

DREQ0 for ASCI transmission and reception respectively. To initiate

memory to/from ASCI DMA transfer, perform the following operations:

1. Load the source and destination addresses into SAR0 and DAR0

Specify the I/O (ASCI) address as follows:

a. Bits A0–A7 must contain the address of the ASCI channel

transmitter or receiver (I/O addresses

6H

-

9H

).

b. Bits A8–A15 must equal 0.

c. Bits SAR17–SAR16 must be set according to Table 16 to enable

use of the appropriate ASCI status bit as an internal DMA

request.

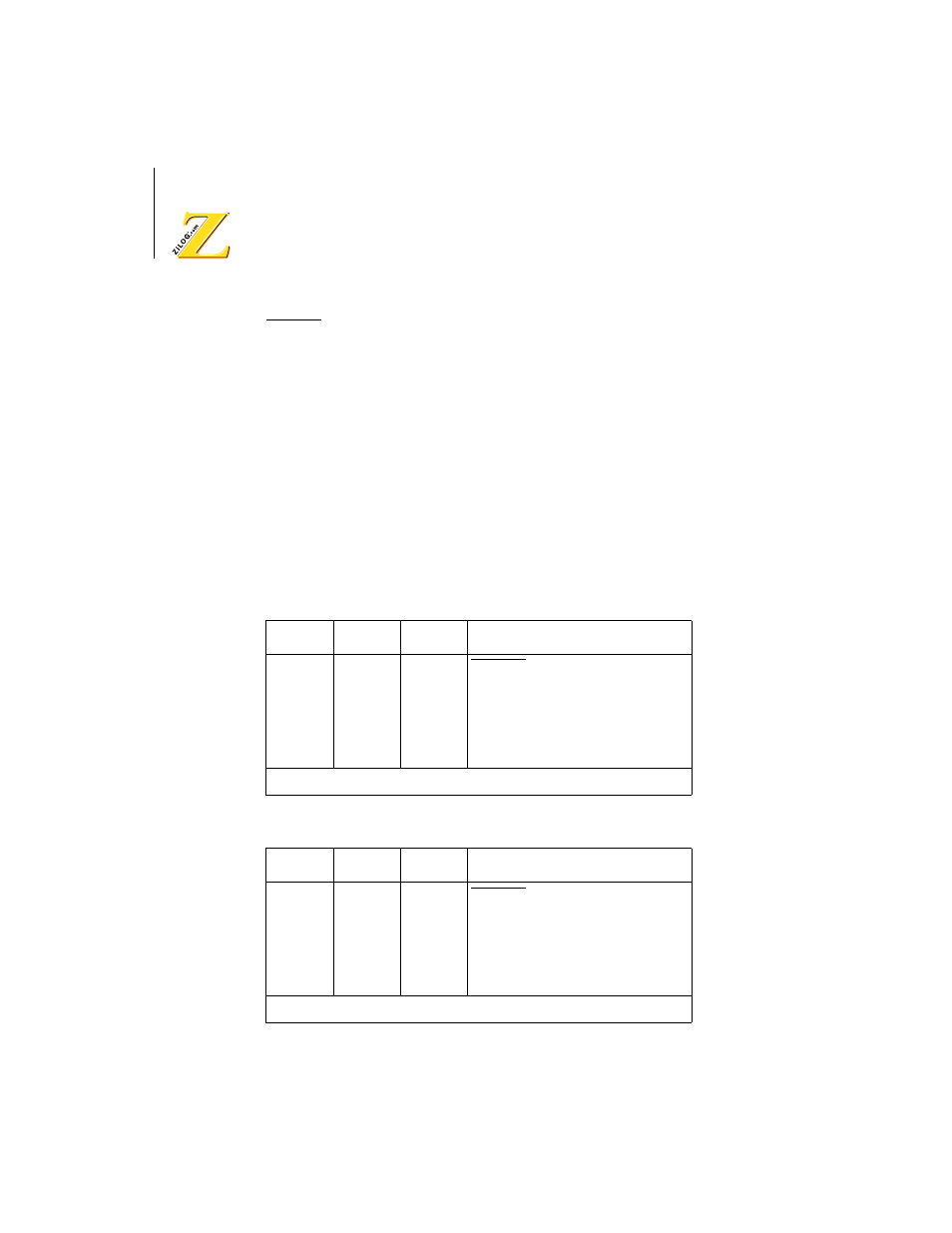

Table 16. DMA Transfer Request

SAR18

SAR17

SAR16 DMA Transfer Request

X

0

0

DREQ0

X

0

1

RDRF (ASCI channel 0)

X

1

0

RDRF (ASCI channel 1)

X

1

1

Reserved

Note: X = Don’t care

DAR18

DAR17

DAR16 DMA Transfer Request

X

0

0

DREQ0

X

0

1

TDRE (ASCI channel O)

X

1

0

TDRE (ASCI channel 1)

X

1

1

Reserved

Note: X = Don’t care