Figure 18. wait timing diagram – Zilog Z80180 User Manual

Page 43

Z8018x

Family MPU User Manual

28

UM005003-0703

externally synchronizing WAIT input transitions with the rising

edge of the system clock.

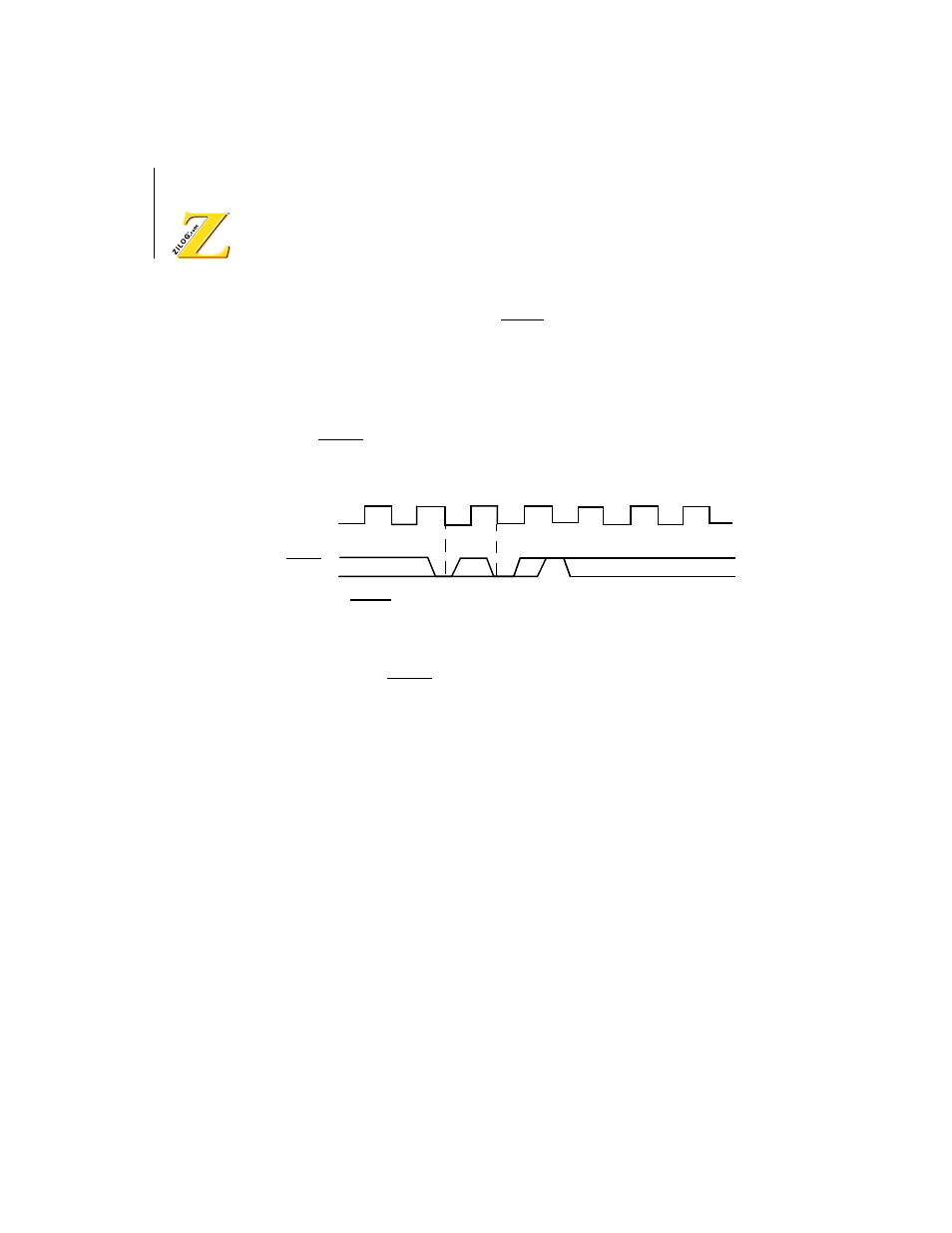

Dynamic RAM refresh is not performed during Wait States (TW) and thus

system designs which use the automatic refresh function must consider

the affects of the occurrence and duration of wait states (TW). Figure 18

depicts WAIT timing.

Figure 18. WAIT Timing Diagram

Programmable Wait State Insertion

In addition to the WAIT input, Wait States (TW) can also be inserted by

program using the Z8X180 on-chip Wait State generator (see Figure 19.

Wait State (TW) timing applies for both CPU execution and on-chip

DMAC cycles.

By programming the four significant bits of the DMA/Wait Control

Register (DCNTL) the number of Wait States, (TW) automatically

inserted in memory and I/O cycles, can be separately specified. Bits 4 and

5 specify the number of Wait States (TW) inserted for I/O access and bits

6 and 7 specify the number of Wait States (TW) inserted for memory

access. These bit pairs all 0–3 programmed Wait States for either I/O or

memory access.

T1

Phi

WAIT

T2

TW

TW

T3

T1