Zilog Z80180 User Manual

Page 83

Z8018x

Family MPU User Manual

68

UM005003-0703

Interrupt Enable Flag 1,2 (IEF1, IEF2)

IEF1 controls the overall enabling and disabling of all internal and

external maskable interrupts (that is, all interrupts except NMI and TRAP.

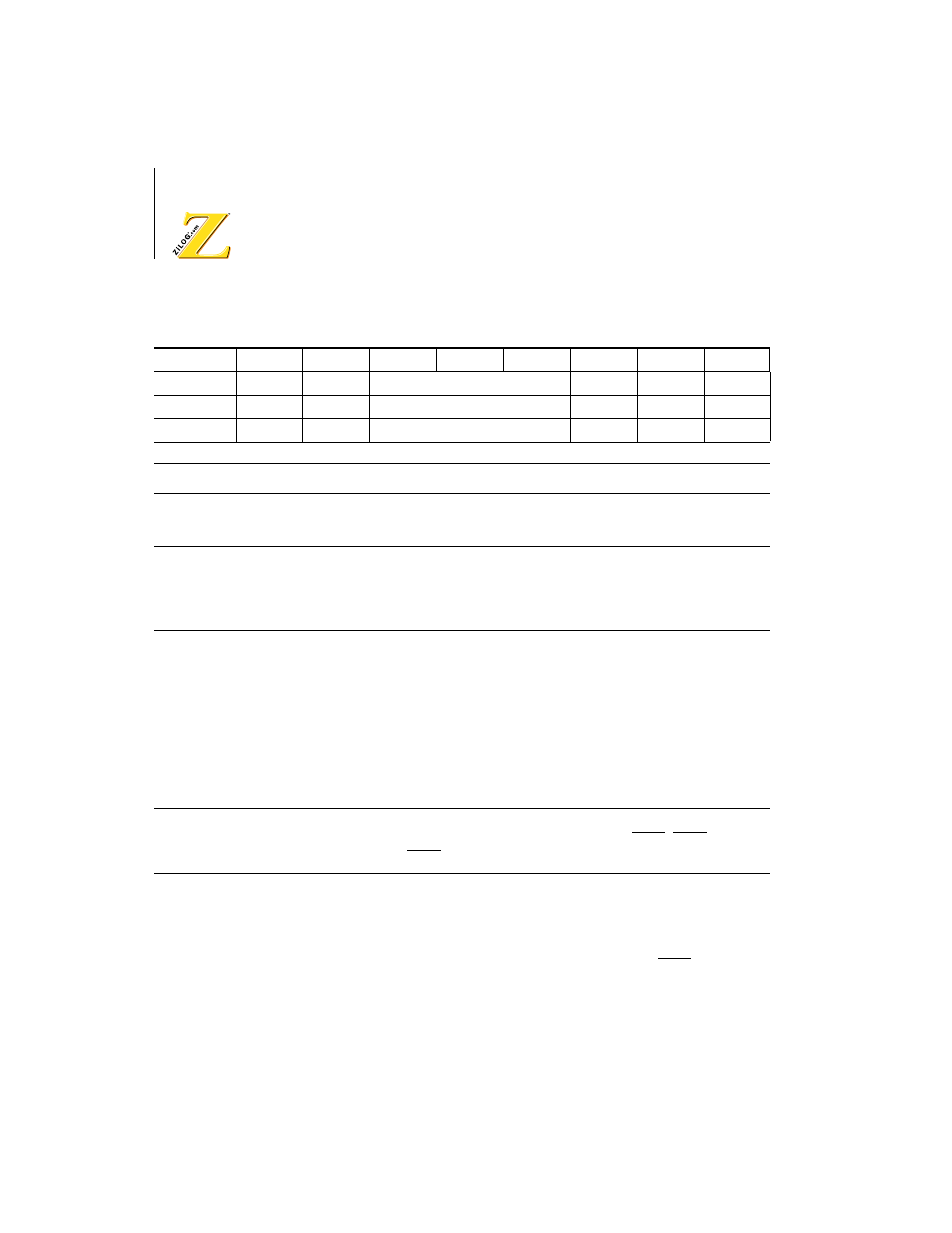

INT/TRAP Control Register (ITC: 34H)

Bit

7

6

5

4

3

2

1

0

Bit/Field

TRAP

UFO

?

ITE2

ITE1

ITE0

R/W

R/W

R

N/A

R/W

R/W

R/W

Reset

0

0

0

0

0

1

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

Bit

Position

Bit/Field

R/W

Value Description

7

TRAP

R/W

This bit is set to 1 when an undefined Op Code is fetched.

TRAP can be reset under program control by writing it

with 0, however, it cannot be written with 1 under

program control.

6

UFO

R

Undefined Fetch Object (bit 6).

When a TRAP interrupt occurs the contents of UFO allow

determination of the starting address of the undefined

instruction. This action is necessary since the TRAP may

occur on either the second or third byte of the Op Code.

UFO allows the stacked PC value to be correctly adjusted.

If UFO = 0, the first Op Code should be interpreted as the

stacked PC-1. If UFO = 1, the first Op Code address is

stacked PC-2.

2

–

0

ITE2

–

0

R/W

Interrupt Enable — ITE2, ITE1 and ITE0 enable and

disable the external interrupt inputs INT2, INT1 and

INT0, respectively. If reset to 0, the interrupt is masked.